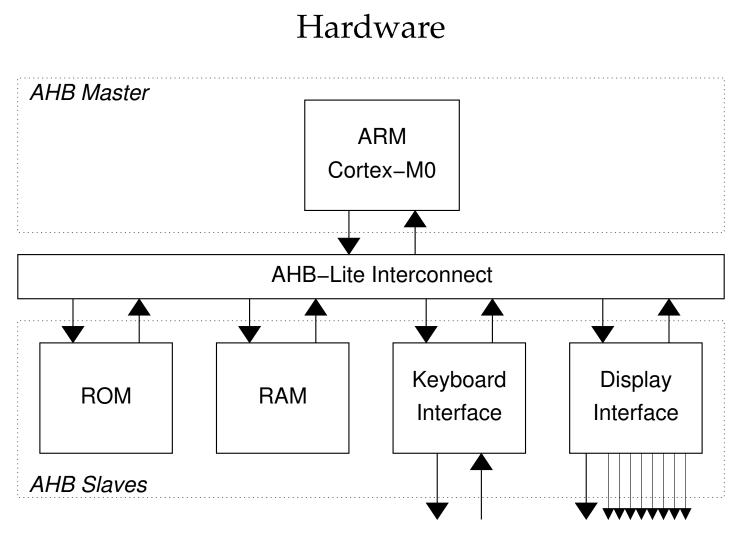

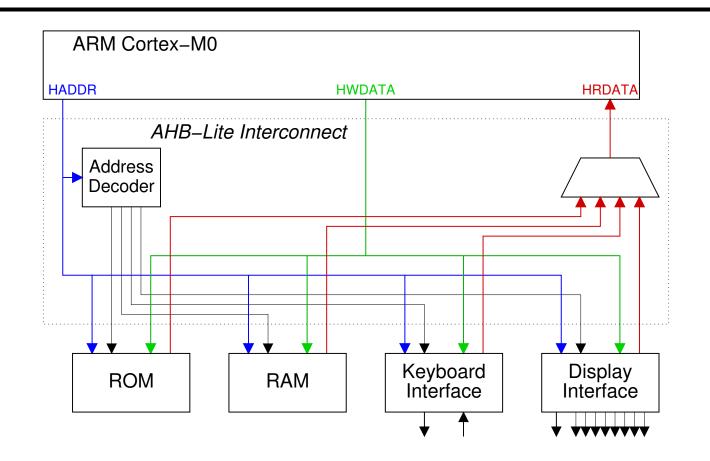

A processor based System-on-Chip will typically include:

## • Hardware

- A processor core (e.g. ARM M0 DesignStart)

- Interconnect (e.g. AHB-Lite bus)

- Fixed program memory (ROM)

- Data memory (RAM)

- Application specific interfaces (for input and ouput)

- Software

- Application specific software (typically written in C)

4002

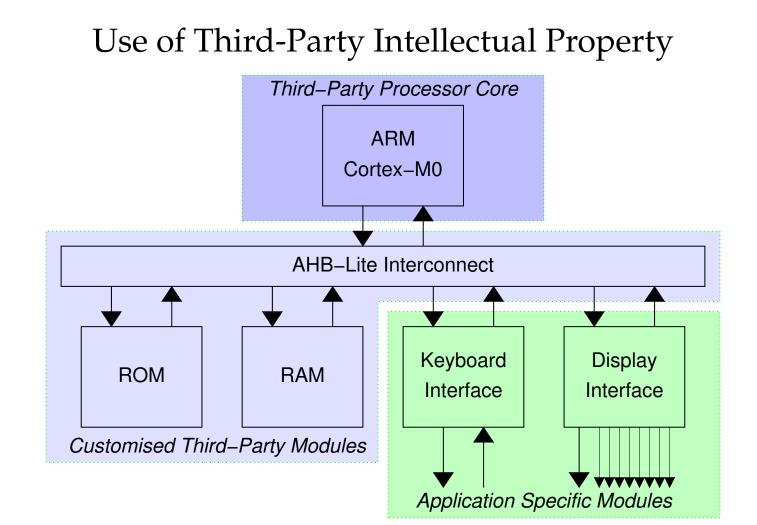

## Use of Third-Party Intellectual Property

The use of hardware and software modules created by others allows designers to build larger and more complex systems.

You may make use of third-party intellectual property in your design provided that:

- 1. You have the permission of the designer

- 2. You acknowledge its use in your report

- 3. You do not remove copyright/licensing notices

In a simple design you might expect to use a third-party processor core together with customised versions of third-party interconnect, ROM and RAM modules

4004

## ARM Cortex-M0 DesignStart

- Simple 32-bit ARM processor core Designed for embedded applications.

- Executes 16-bit instructions from the ARM Thumb2 instruction set

Supported by standard GNU compilers.

• Obfuscated Verilog Source Code

Designed to be usable but not to be reverse engineered or customised.

• Available free for academic and other non-commercial use You may use the provided core for this project. If you wish the Cortex-M0 DesignStart for another purpose, you should apply to ARM for permission.

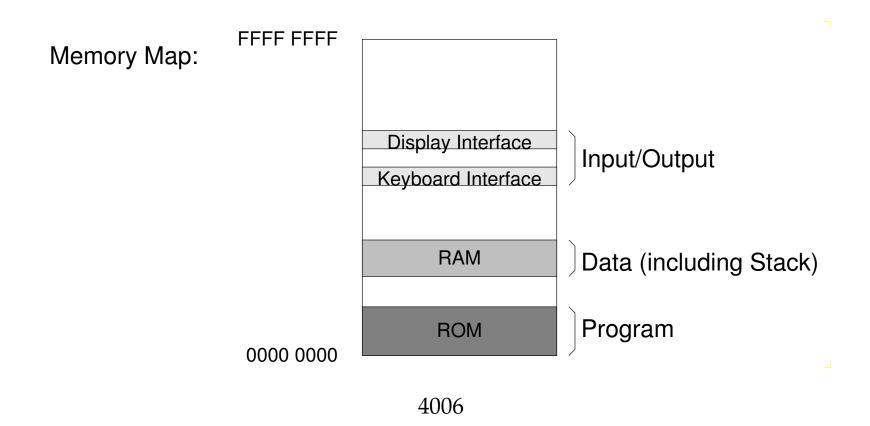

## Programmers View - Memory Mapped I/O

The programmer sees each input/output device as occupying one or more memory locations.

## I/O Devices

13002

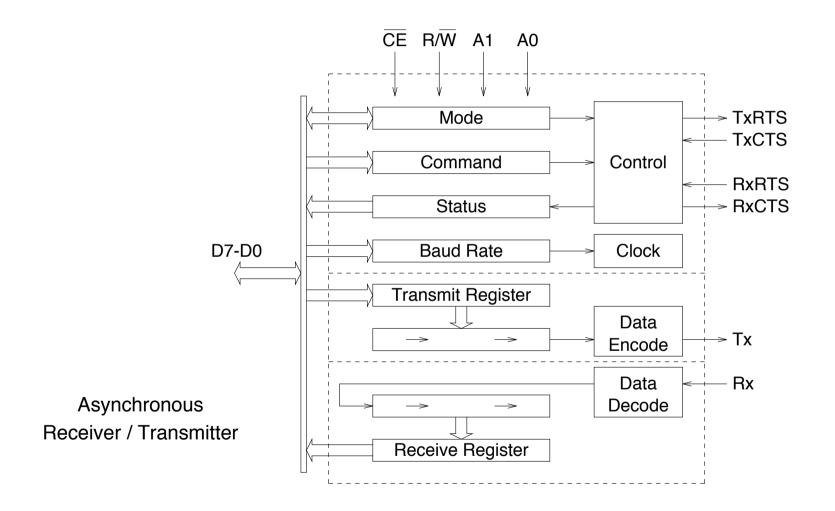

The registers of the asynchronous receiver/transmitter chip<sup>1</sup> are located at the following addresses.

| A1,A0 | Read             | Write             |

|-------|------------------|-------------------|

| 00    | Mode             | Mode Select       |

| 01    | Status           | Baud Rate Select  |

| 10    | NOT USED         | Command           |

| 11    | Receive Register | Transmit Register |

Register access modes

- read/write

- read only

- write only

- no direct access at all

<sup>&</sup>lt;sup>1</sup>This chip is loosely based on the SCN2681 DUART as used on ECS SPARCboards.

Although memory mapped, these registers do not act merely as memory locations used to transfer data. The action of accessing a register provides information to the device.

- Write to *Transmit register* triggers the output of data even if the data in the register is not changed.

- Read from *Receive register* indicates that the data is no longer required so that it may be overwritten.

- Data in the *Command register* is only consulted during a write, its effect is immediate e.g. reset transmit machine.

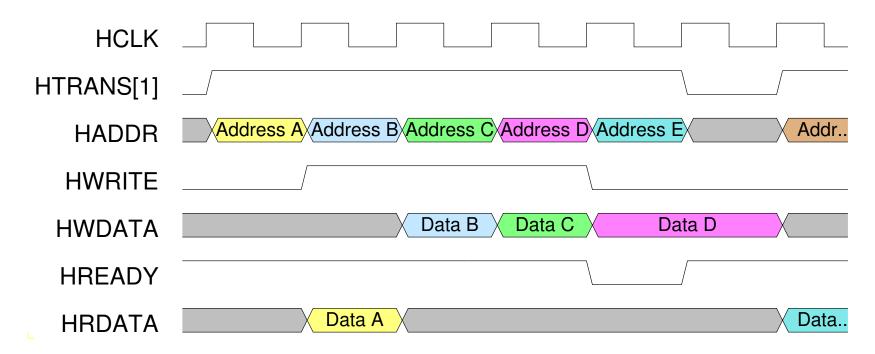

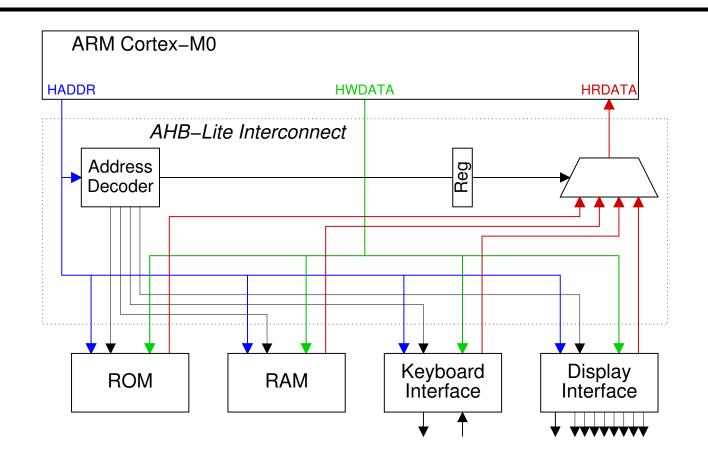

### AHB-Lite Bus

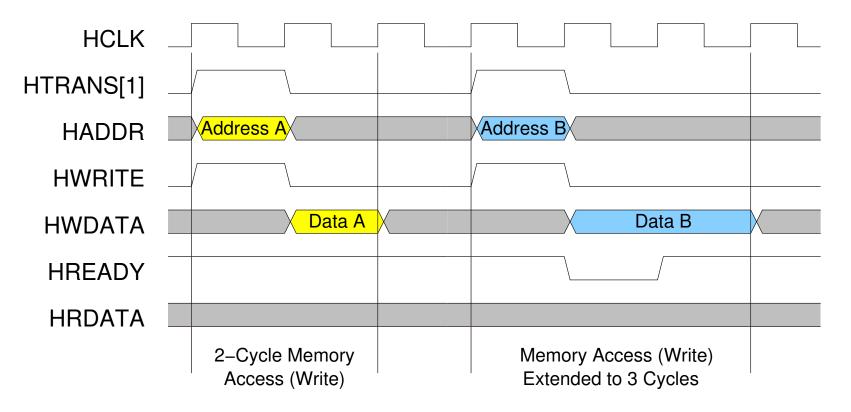

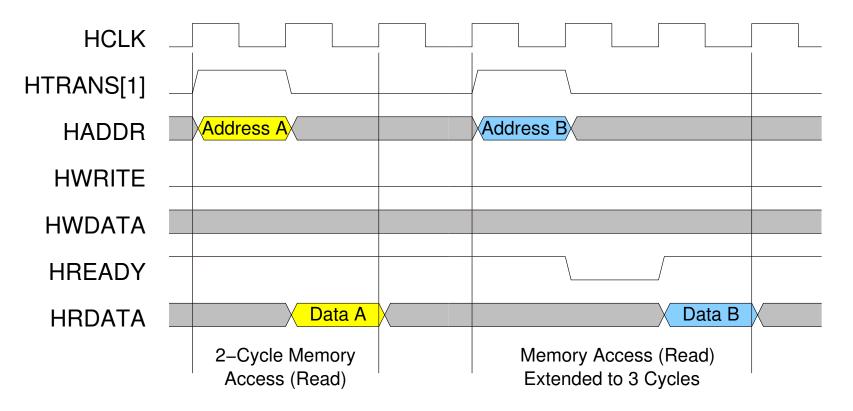

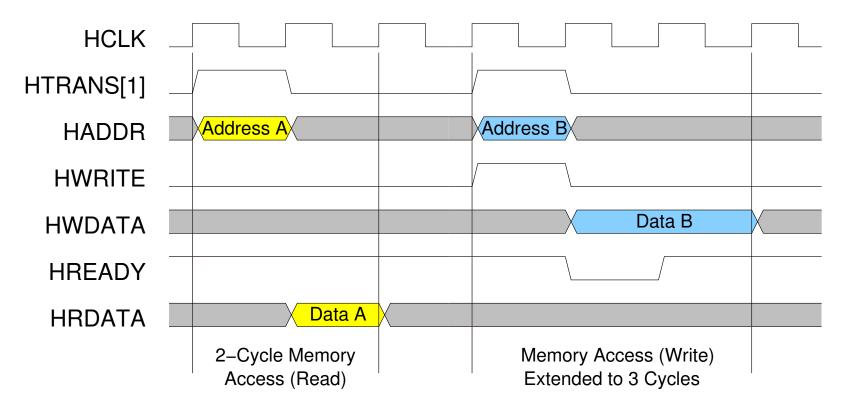

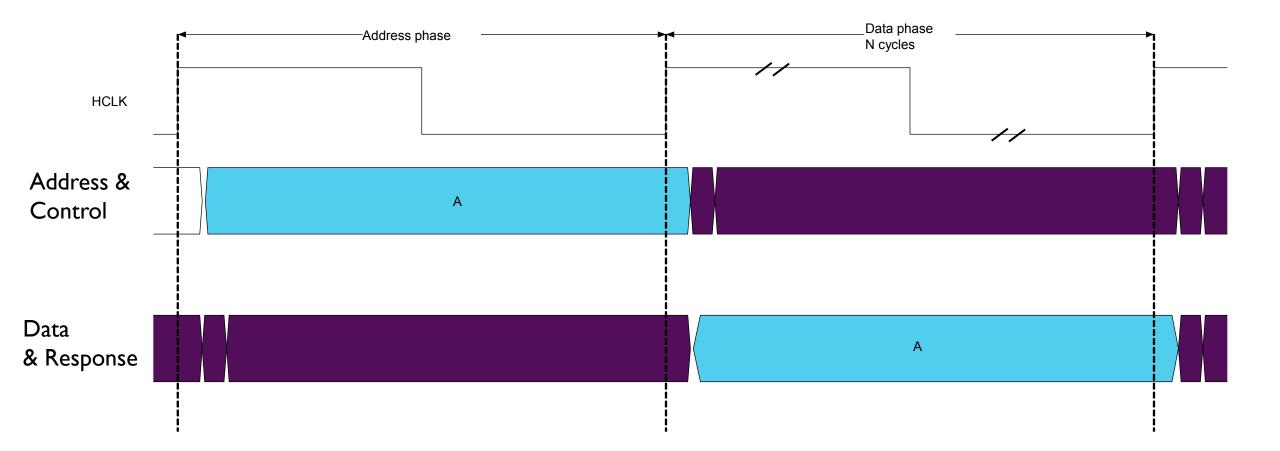

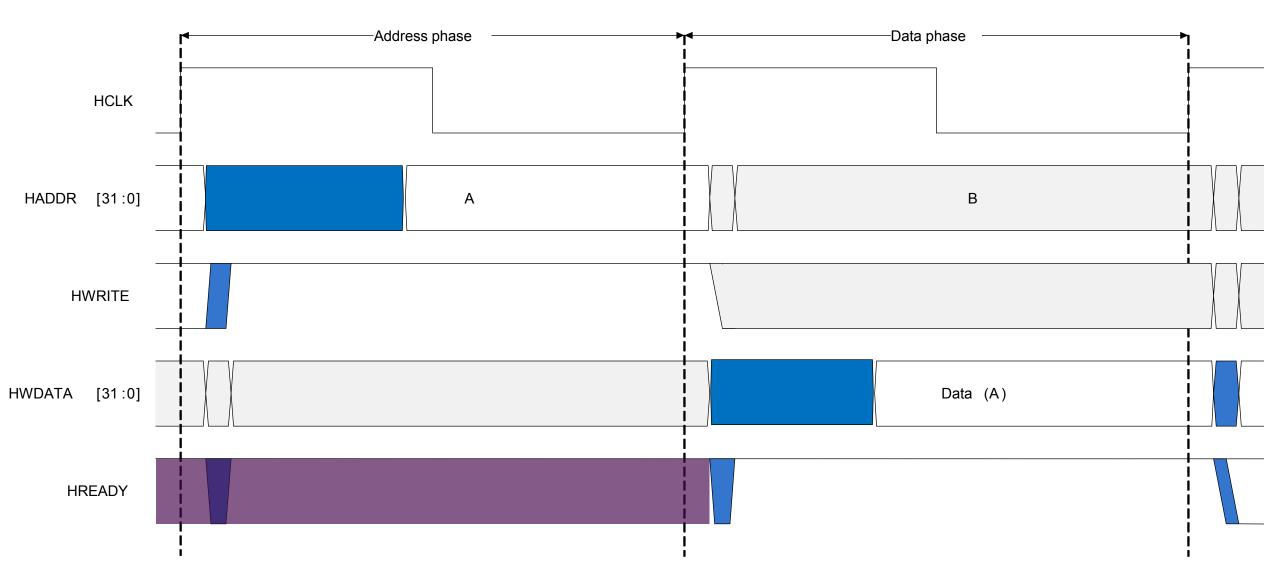

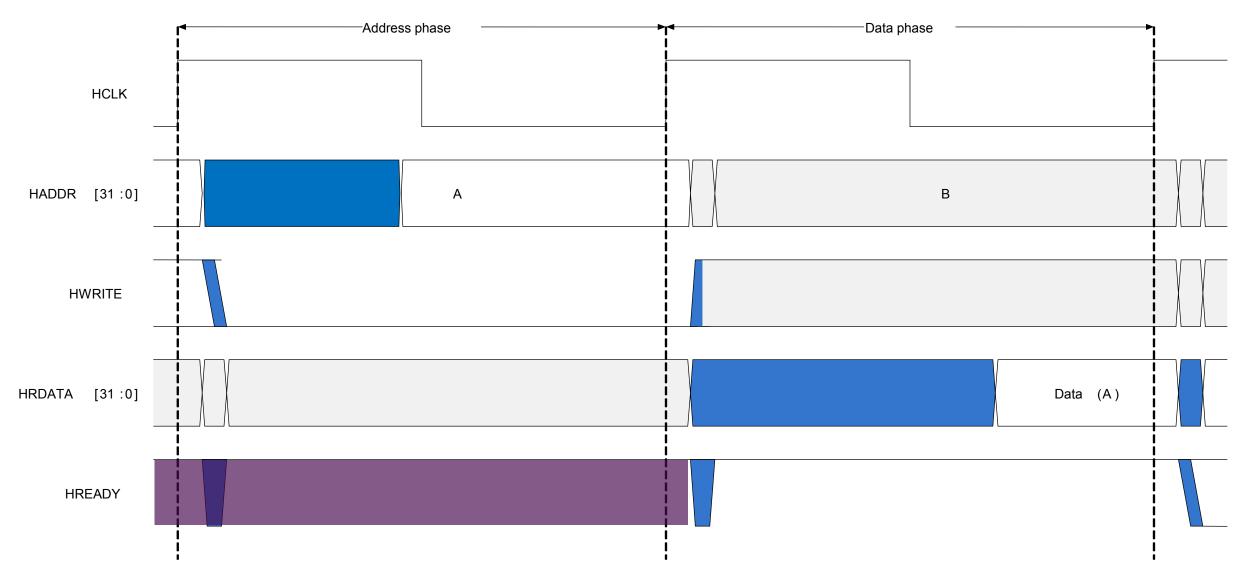

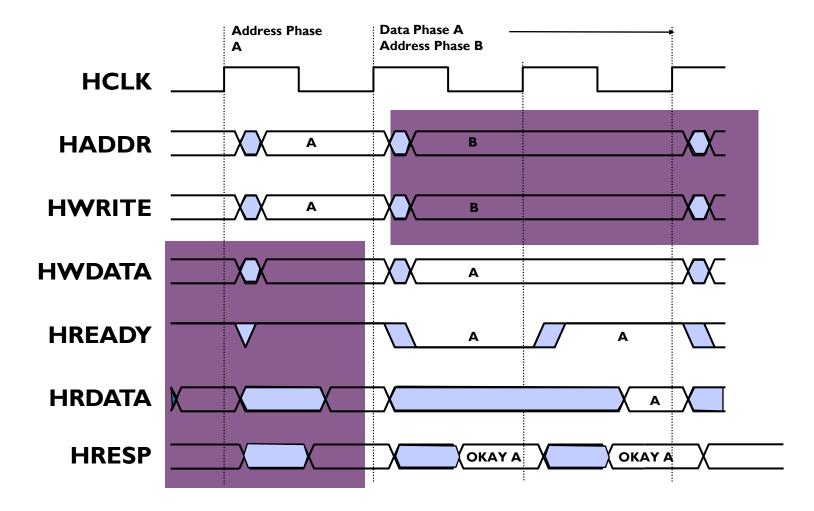

Each memory access takes two or more clock cycles

### AHB-Lite Bus

Each memory access takes two or more clock cycles

### AHB-Lite Bus

Each memory access takes two or more clock cycles

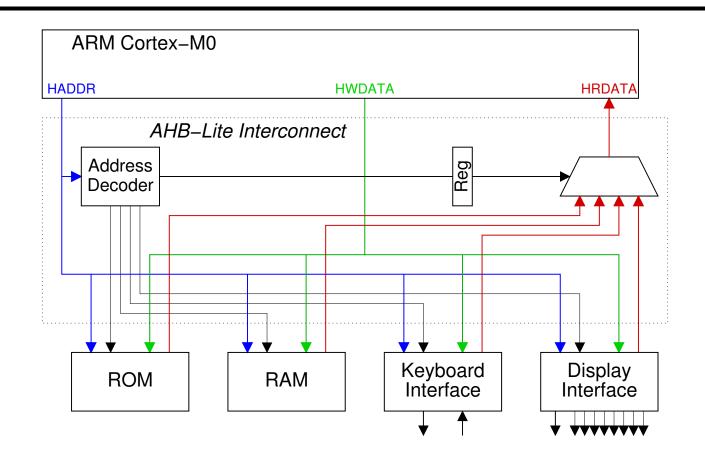

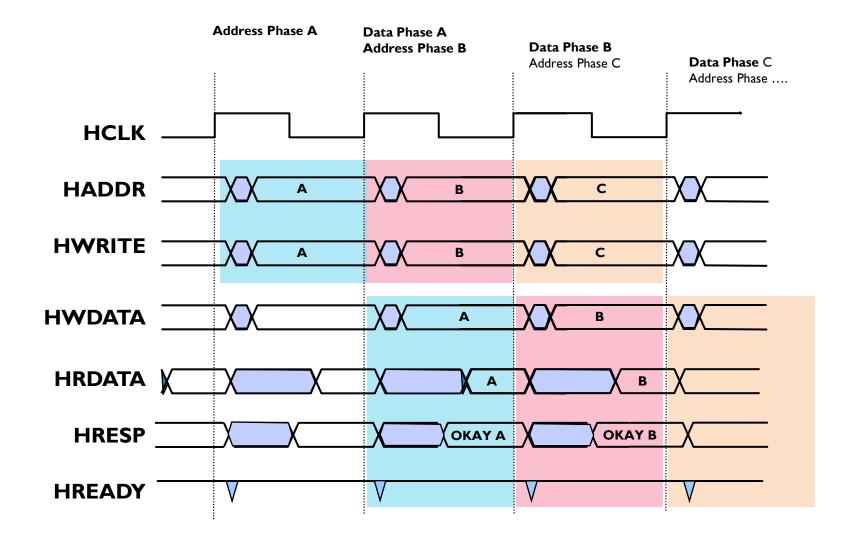

### **AHB-Lite Bus**

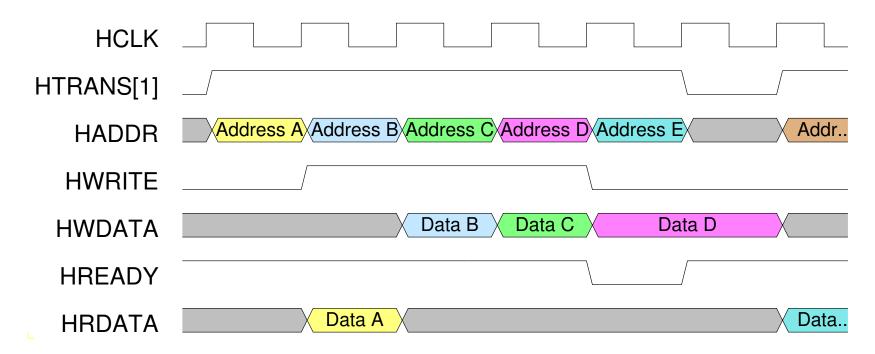

Memory accesses can be pipelined<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>the address phase of one memory access may start before the data phase of the previous access is complete

### **AHB-Lite Bus**

Memory accesses can be pipelined<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>the address phase of one memory access may start before the data phase of the previous access is complete

### **AHB-Lite Bus**

Memory accesses can be pipelined<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>the address phase of one memory access may start before the data phase of the previous access is complete

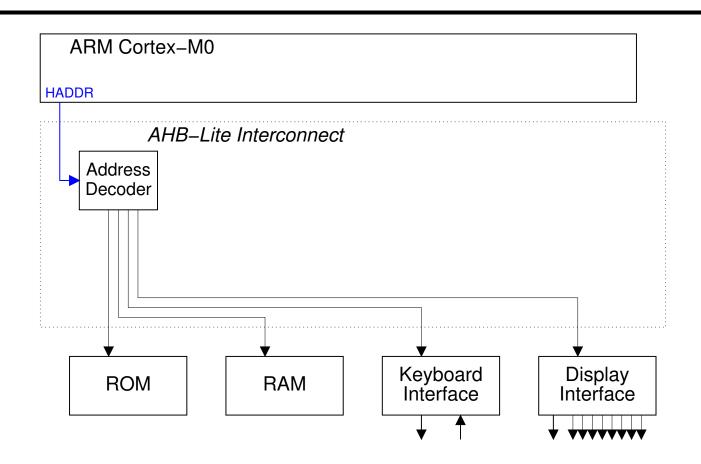

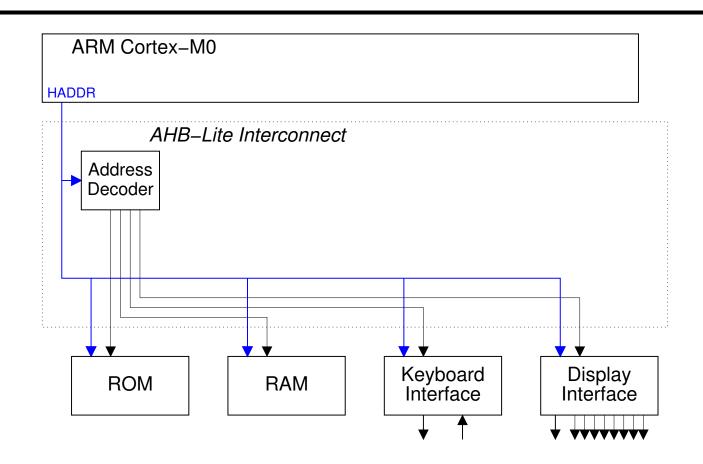

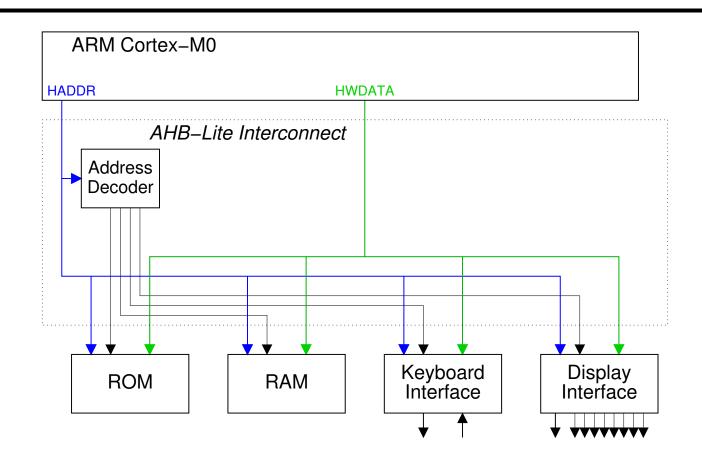

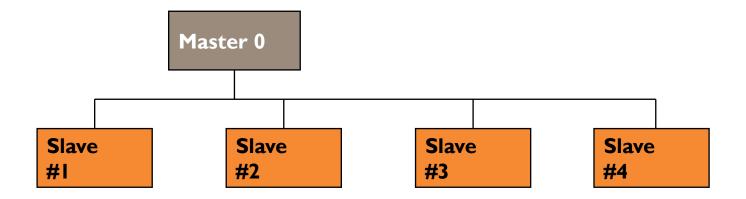

| ARN | / Cortex–M0 | )                |                       |                      |

|-----|-------------|------------------|-----------------------|----------------------|

|     | AHB-L       | ite Interconnect |                       |                      |

|     |             |                  |                       |                      |

|     |             |                  |                       |                      |

|     |             |                  |                       |                      |

|     | ROM         | RAM              | Keyboard<br>Interface | Display<br>Interface |

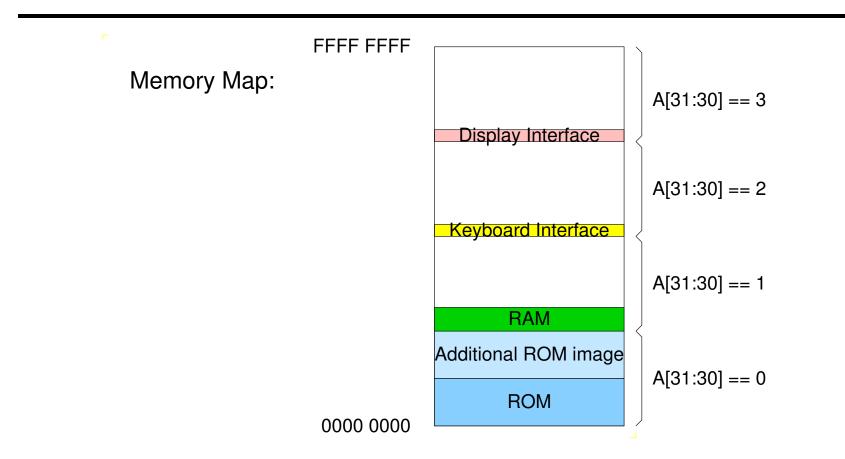

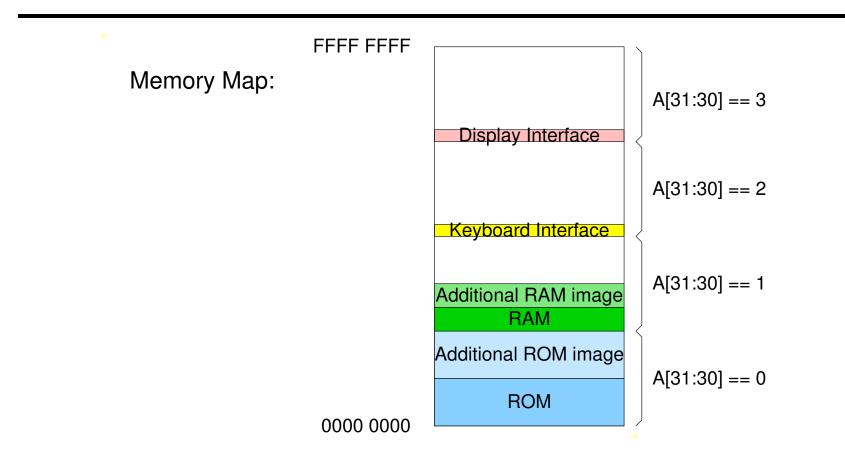

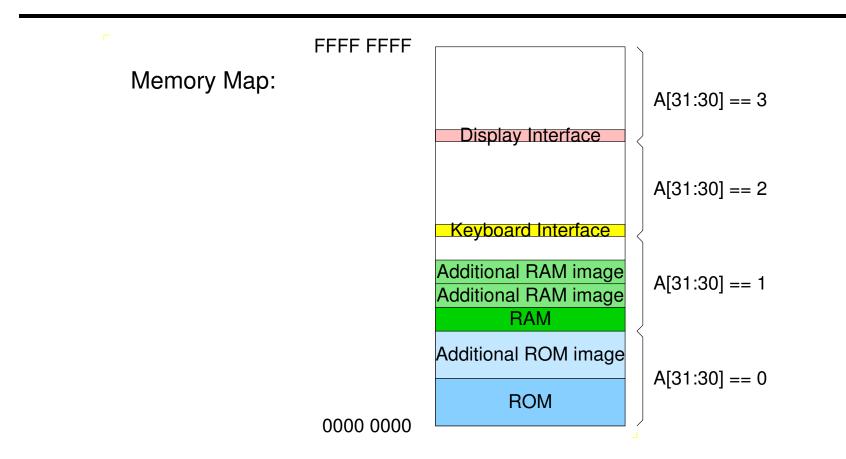

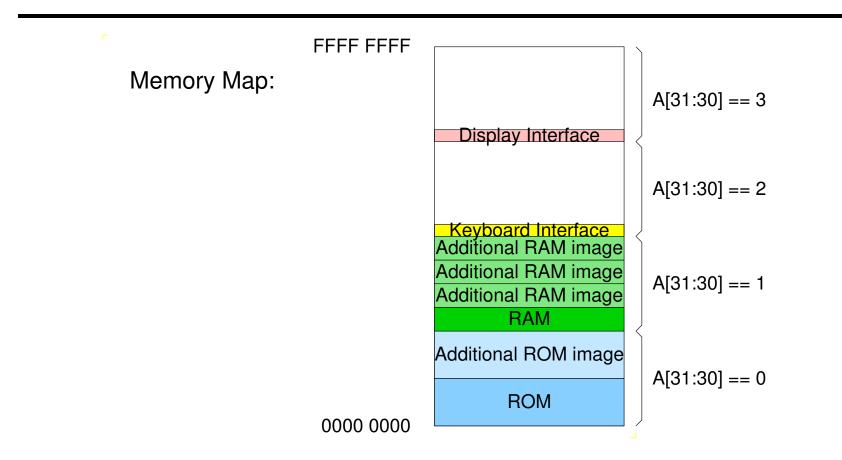

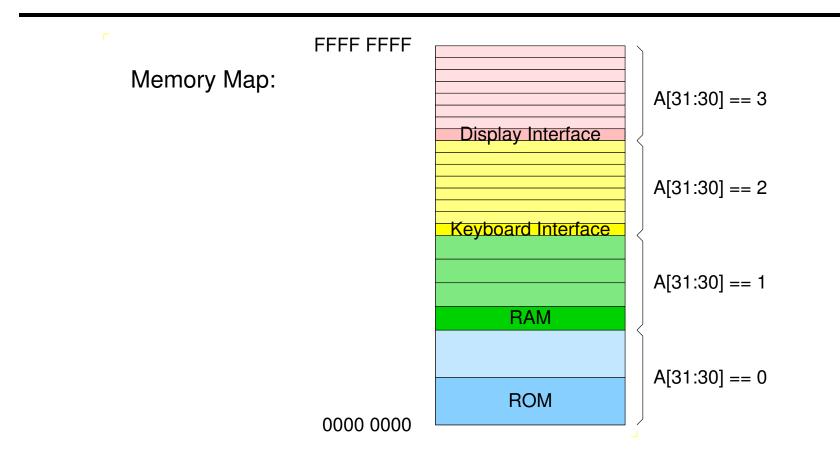

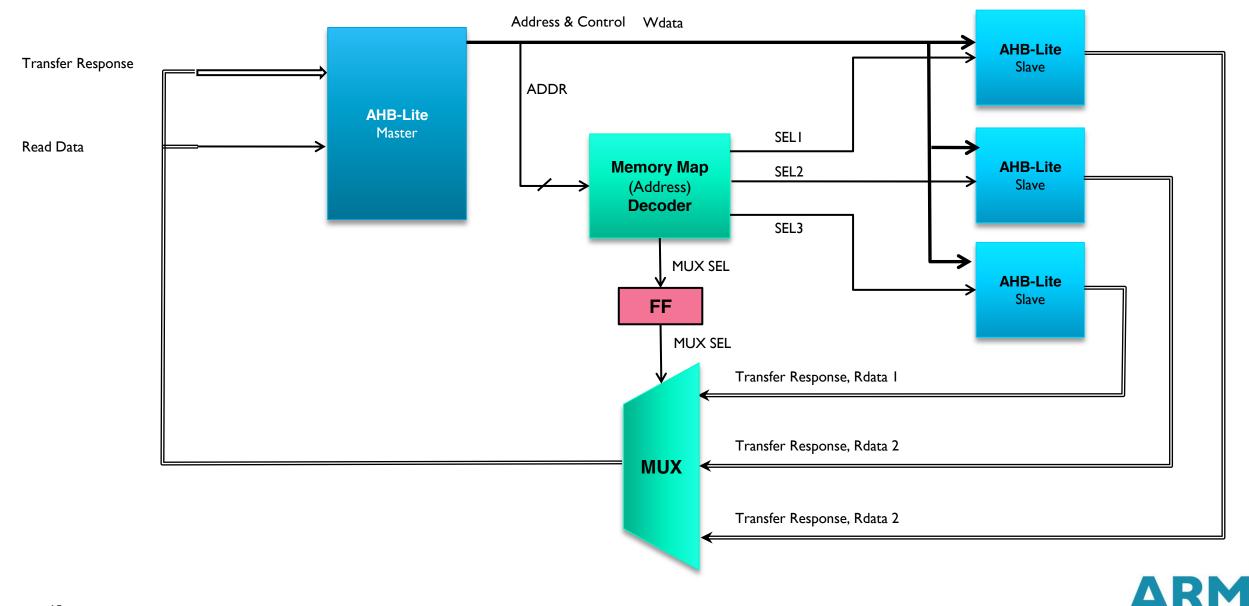

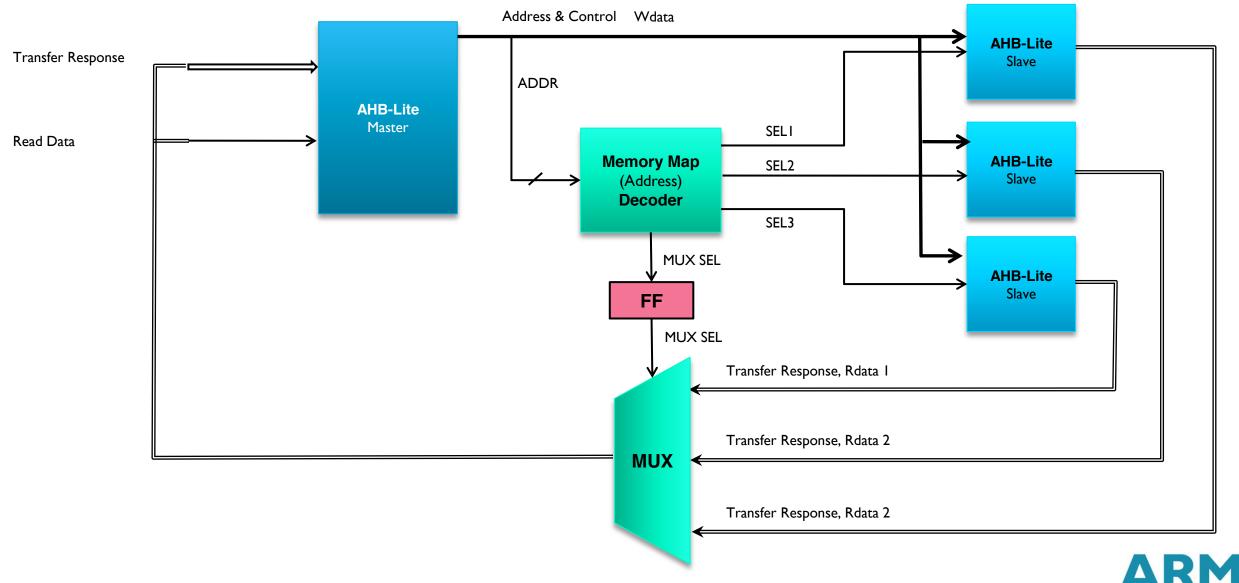

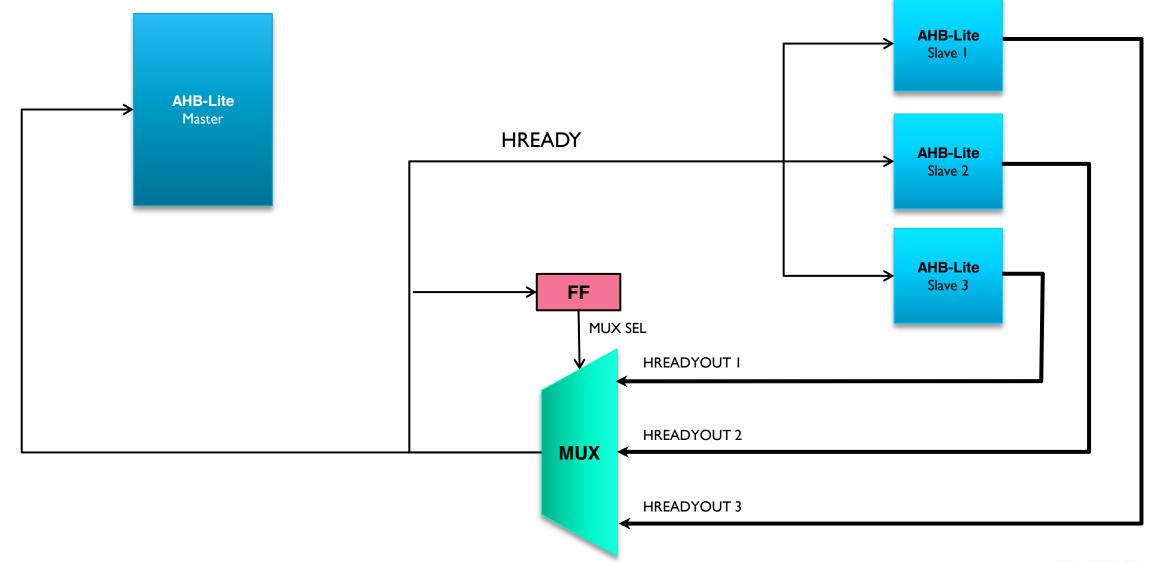

• Individual slave select signals are generated from the high order bits of HADDR

• The low order bits of HADDR are used to select registers within the slaves

• The write data (HWDATA) is broadcast to all of the slaves

• A multiplexer selects the read data (HRDATA) from one of the slaves

• The Address Decoder controls the multiplexer via a register which adds a single cycle delay

#### **AHB-Lite Interconnect**

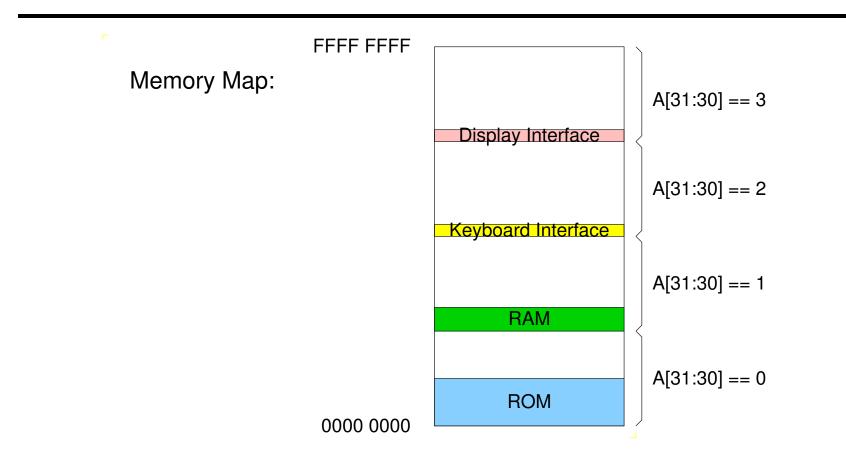

showing HADDR, HWDATA, HRDATA and individual slave HSEL select signals.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

- With partial address decoding we use fewer address lines (A31 and A30 in the example above) and less logic for decoding.

- A side effect of this is that we get multiple images of some or all of the slave devices.

# ARM<sup>®</sup> AMBA<sup>®</sup> 3 AHB-Lite

Overview

The Architecture for the Digital World®

## ARM<sup>®</sup> AMBA<sup>®</sup> Open Specification

- Open standard (No License required)

- The de facto standard for on-chip communication

- Used as on-chip interconnect for connecting and managing functional blocks in a System-on-Chip

- Promotes design re-use by defining common interface standards for SoC modules

- AMBA Family: AMBA 5, AMBA 4, AMBA 3 & AMBA 2

- AMBA 5 CHI (Coherent Hub Interface) specification is the latest addition to the AMBA (mainly used for server and networking SoCs)

- More info: <u>http://www.arm.com/products/system-ip/amba/amba-open-specifications.php</u>

## **AMBA** Acronyms

### Acronyms

- $AMBA^{\mathbb{R}} \rightarrow Advanced Microcontroller Bus Architectures$

- AXI  $\rightarrow$  Advanced eXtensible Interface

- ACE  $\rightarrow$  AXI Coherency Extensions

- AHB  $\rightarrow$  Advanced High-Performance Bus

- APB  $\rightarrow$  Advanced Peripheral Bus

- ATB  $\rightarrow$  Advanced Trace Bus

- ASB  $\rightarrow$  Advanced System Bus

## How to access the full specification?

Go to <u>http://infocenter.arm.com/</u>

| center.arm.com/help/index.jsp  Center.arm.com/help/index.jsp  The Architecture for the Digital World®         |                                                      |                                  |                                                                                          |          |                  |                          |  |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------|----------|------------------|--------------------------|--|

|                                                                                                               | Support                                              | Community                        | Markets                                                                                  | About    | Careers          |                          |  |

| You are here: 💧 🔸 Su                                                                                          | pport > Docun                                        | nentation                        |                                                                                          |          |                  |                          |  |

| All documents                                                                                                 |                                                      | <ul> <li>Search our d</li> </ul> | Search our documentation                                                                 |          | 🔊 🛛 Search scope | Search scope: All topics |  |

| Contents                                                                                                      | Roj 🗖                                                | АМВА                             |                                                                                          |          |                  |                          |  |

| <ul> <li>ARM11 processo</li> <li>ARM9 processors</li> <li>ARM7 processors</li> <li>ARM7 processors</li> </ul> | s<br>s                                               |                                  | This document is only available in a PDF version to registered ARM customers.            |          |                  |                          |  |

| AMBA specificati                                                                                              |                                                      |                                  | Copyright © 2008 ARM Limited. All rights reserved.<br>Non-Confidential Restricted Access |          |                  |                          |  |

| AMBA 4 and .     AMBA 3     Multi-laye                                                                        |                                                      | Non-Confide                      | ential Restricte                                                                         | d Access |                  | DF version               |  |

|                                                                                                               | TB Protocol<br>PB Protocol<br>HB-Lite Pro<br>ownload | Home                             |                                                                                          |          |                  |                          |  |

## AMBA 3 AHB-Lite

- Original AHB Specification was part of AMBA 2

- Subset of original AHB

- Reduced interconnect logic

- Simplifies slave design

- Master slave architecture

- Most of the designs have single master in the system

- Multiple masters still possible on multi-layer interconnect

## AMBA 3 AHB-Lite

**ARM**

Image Source: Walt Disney

## AMBA 3 AHB-Lite

- Single Master

- Simple slaves

- Easier module design/debug

- No arbitration issues

Image Source: Walt Disney

## **AHB-Lite transactions**

- Master

- Register Read

- Register Write

- Burst Read

- Burst Write

- Slave/Peripheral

- Can make Master wait

- Can give error response

Image Source: Walt Disney

### **AHB-Lite Features**

- Single Clock Edge operation

- Uni-directional busses

- No tri-state signals

- Good for synthesis

- Pipelined Operation

# A system based on AHB-Lite

## **Components of AHB-Lite System**

- Master

- Slaves/Peripherals

- Address Decoder

Multiplexor

AHB-Lite Interconnect

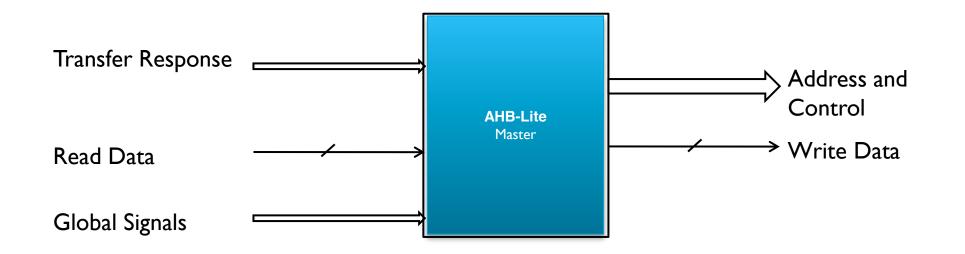

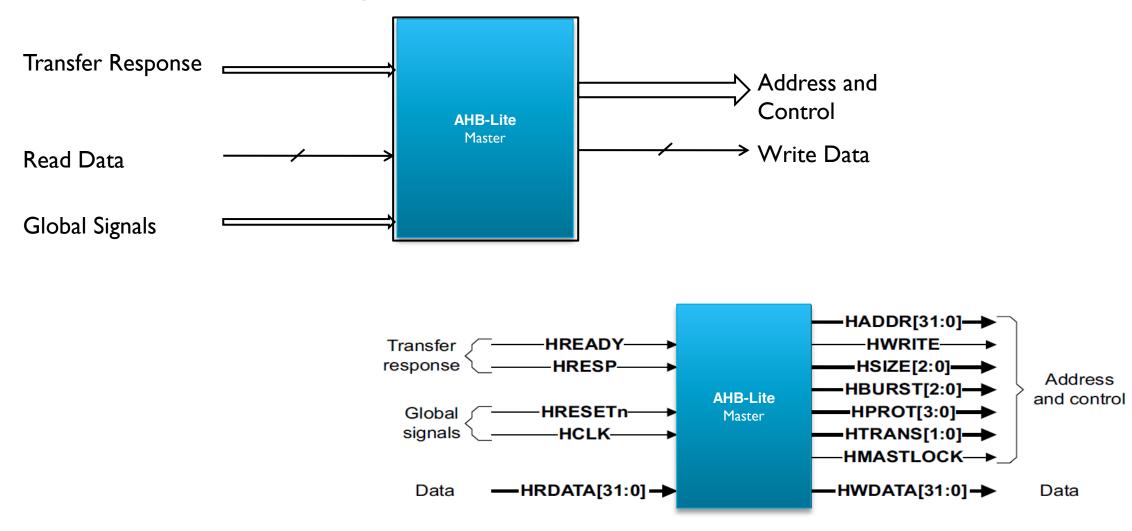

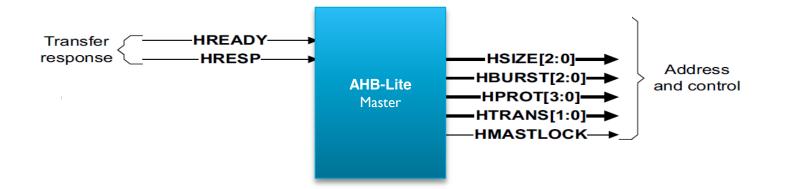

### **AHB-Lite Master**

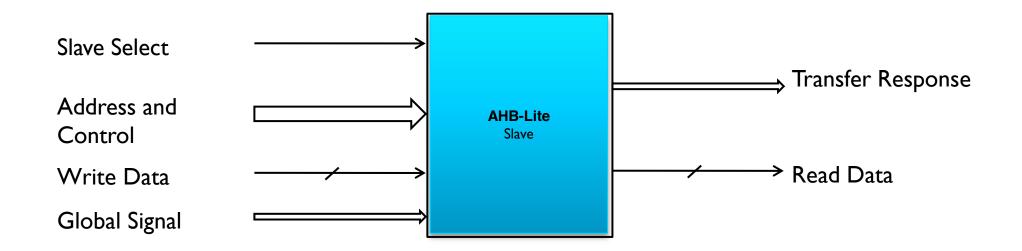

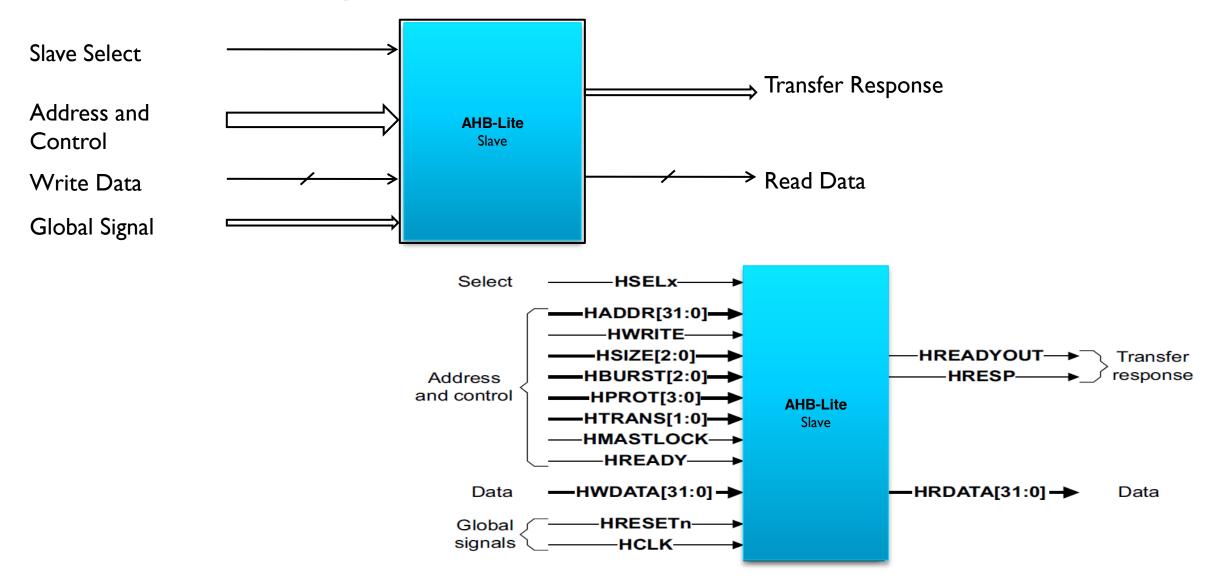

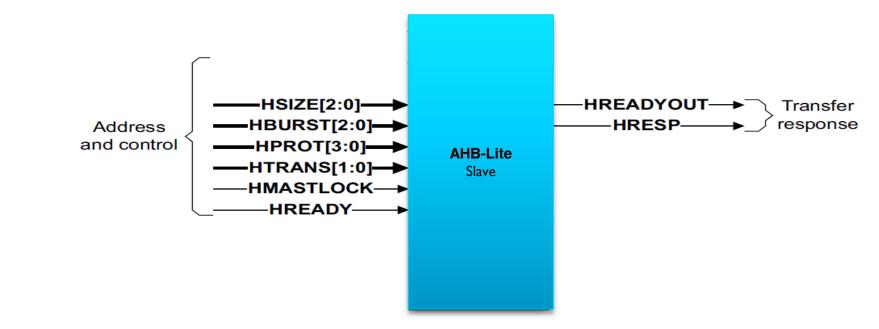

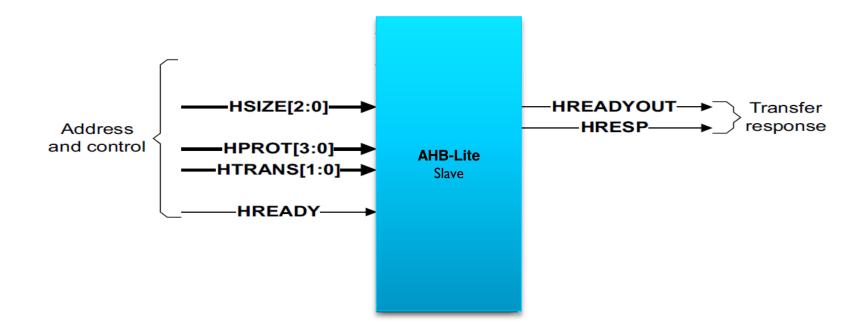

### **AHB-Lite Slave**

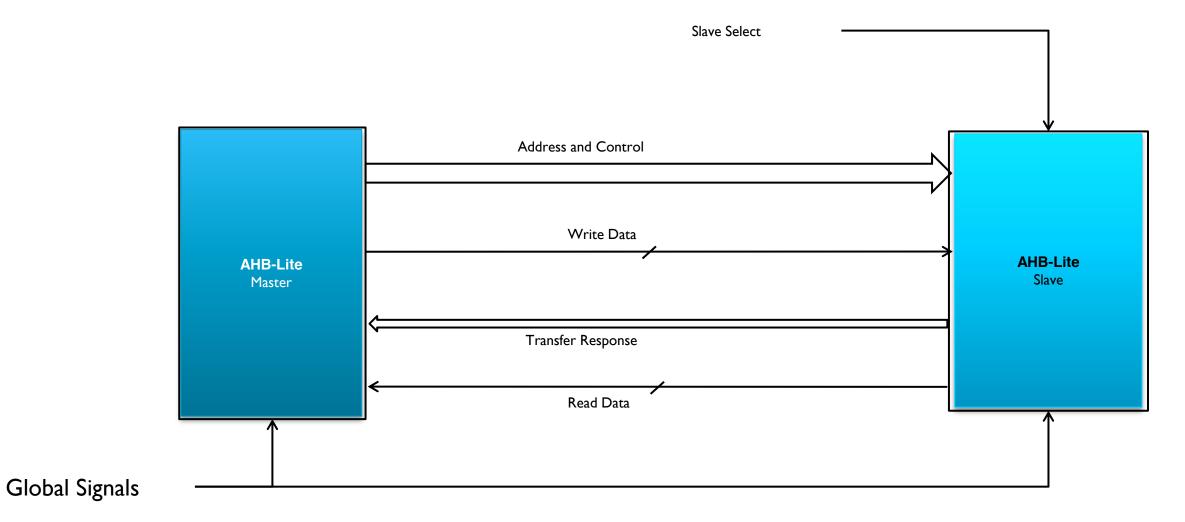

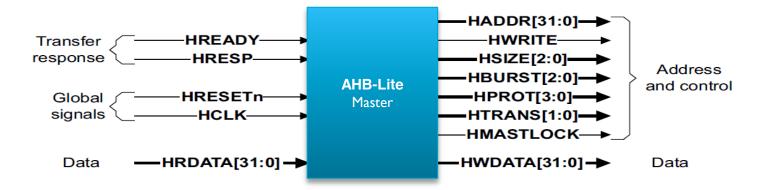

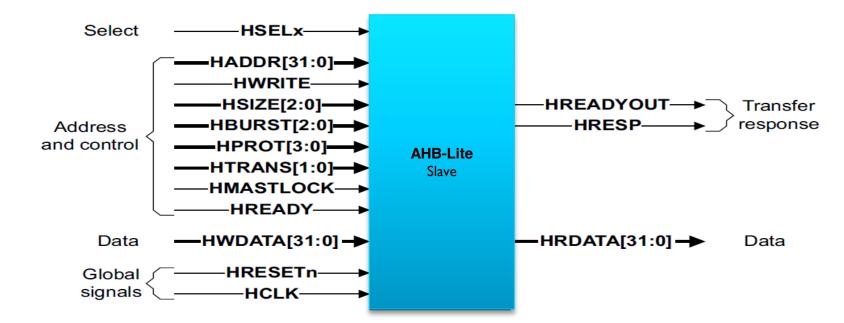

### AHB-Lite Master & Slave

**ARM**

### Decoder & MUX

### Pipelined Transactions (Conceptual Level)

# **AHB-Lite Signals**

## **AHB-Lite Master Signals**

### **AHB-Lite Slave Signals**

### **AHB-Lite Master & Slave**

### AHB-Lite Master & Slave

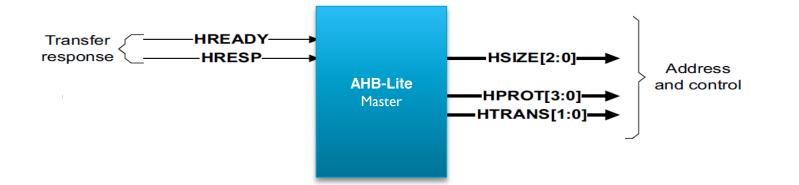

### Cortex M0 doesn't speak the entire language !

- Cortex M0 does not support BURST transaction

- HBURST[2:0] is always 3'b000

- Cortex M0 does not support locked transactions

- HMASTLOCK is always 1'b0

- Cortex M0 issues only non-sequential transfers

- HTRANS[1:0] is either 2'b00 (IDLE) or 2'b10 (Non Sequential)

### AHB-Lite Master & Slave

# HTRANS[1:0]

| HTRANS | Туре    | Description                                                                                                                                                                  |  |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00     | IDLE    | Master does not wish to perform a transfer                                                                                                                                   |  |

| 0      | BUSY    | Bus Master is in the middle of a<br>burst but cannot immediately continue<br>with the next transfer                                                                          |  |

| 10     | NON-SEQ | Indicates the first transfer of a burst or a single transfer                                                                                                                 |  |

| 11     | SEQ     | The remaining transfers in the burst are<br>sequential address steps from the previous<br>transfer. Step size is that of data width of<br>transfer (which is shown by HSIZE) |  |

Cortex M0 Always generates NON-SEQ Transactions

| Address-phase: |                | Data-phase:       |                   |                  |                 |

|----------------|----------------|-------------------|-------------------|------------------|-----------------|

| HSIZE<br>[1:0] | HADDR<br>[1:0] | HxDATA<br>[31:24] | HxDATA<br>[23:16] | HxDATA<br>[15:8] | HxDATA<br>[7:0] |

| 00             | 00             | -                 | -                 | -                | Rd[7:0]         |

| 00             | 01             | -                 | -                 | Rd[7:0]          | -               |

| 00             | 10             | -                 | Rd[7:0]           | -                | -               |

| 00             | 11             | Rd[7:0]           | -                 | -                | -               |

| 01             | 00             | -                 | -                 | Rd[15:8]         | Rd[7:0]         |

| 01             | 10             | Rd[15:8]          | Rd[7:0]           | -                | -               |

| 10             | 00             | Rd[31:24]         | Rd[23:16]         | Rd[15:8]         | Rd[7:0]         |

# HPROT[3:0] Protection Signal Encoding

| HPROT[3]<br>Cacheable | HPROT[2]<br>Bufferable | HPROT[1]<br>Privileged | HPROT[0]<br>Data/Opcode | Description       |

|-----------------------|------------------------|------------------------|-------------------------|-------------------|

| -                     | -                      | -                      | 0                       | Opcode fetch      |

| -                     | -                      | -                      | 1                       | Data access       |

| -                     | -                      | 0                      | -                       | User access       |

| -                     | -                      | 1                      | -                       | Privileged access |

| -                     | 0                      | -                      | -                       | Non-bufferable    |

| -                     | 1                      | -                      | -                       | Bufferable        |

| 0                     | -                      | -                      | -                       | Non-cacheable     |

| 1                     | -                      | -                      | -                       | Cacheable         |

### Transactions

| Transaction  | Access  |       |

|--------------|---------|-------|

| HTRANS[1:0]  | = 2'b00 | IDLE  |

| HTRANS [1:0] | = 2'b10 | FETCH |

| HPROT[0]     | = 1'b0  |       |

| HSIZE[1:0]   | = 2'b10 |       |

| HWRITE       | = 1'b0  |       |

Instruction Fetch

| Transaction  |                 | Access |

|--------------|-----------------|--------|

| HTRANS [1:0] | = 2'b10         | BYTE   |

| HPROT[0]     | = 1'b1          |        |

| HSIZE[1:0]   | = 2'b00         |        |

| HTRANS [1:0] | = 2'b10         | HALF-  |

| HPROT[0]     | = 1 <b>′</b> b1 | WORD   |

| HSIZE[1:0]   | = 2'b01         |        |

| HTRANS [1:0] | = 2'b10         | WORD   |

| HPROT[0]     | = 1'b1          |        |

| HSIZE[1:0]   | = 2'b10         |        |

|              |                 |        |

# **Control Signals Recap**

#### HTRANS[1:0]

IDLE BUSY NONSEQ SEQ

#### HBURST[2:0]

SINGLE INCR WRAP[4|8|16] INCR[4|8|16]

#### **HMASTLOCK**

UNLOCKED LOCKED

#### HSIZE[2:0]

Byte Halfword Word Doubleword

...

HPROT[3:0]

Data/Opcode Privileged/user Bufferable Cacheable

# Transfer Response Signals

| HREADYOUT | Multiplexor | When HIGH, the <b>HREADYOUT</b> signal indicates that a transfer has finished on the bus. This signal can be driven LOW to extend a transfer.                                                                                                                                                                             |

|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRESP     | Multiplexor | The transfer response, after passing through the multiplexor, provides the master<br>with additional information on the status of a transfer.<br>When LOW, the <b>HRESP</b> signal indicates that the transfer status is OKAY.<br>When <b>HIGH</b> , the <b>HRESP</b> signal indicates that the transfer status is ERROR. |

# **AHB-Lite Transactions**

# Basic transfer - Write

# Basic transfer - Read

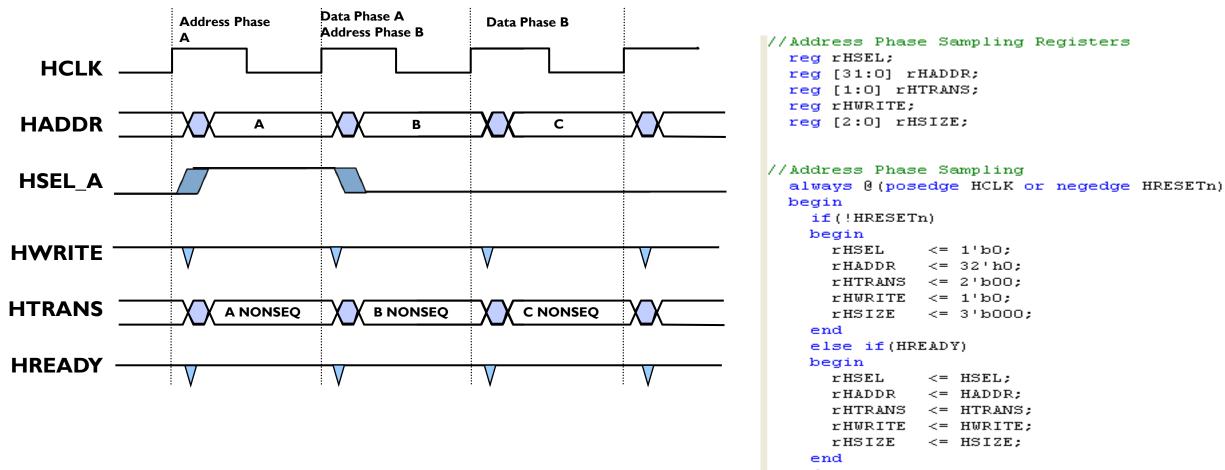

# **AHB** Pipelined Transaction

**ARM**

# **Pipelined Operation**

### AHB basic signal timing – Adding wait states

Master will extend Address Phase B

# HREADY (Inform all)

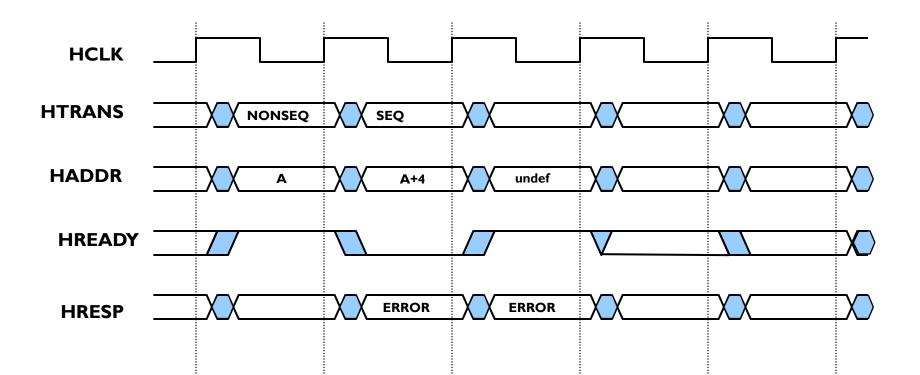

### HRESP – Slave Response

| <u>HRESP</u> | <u>Event</u>                               | <b>Bus Master operation</b>                                                      |

|--------------|--------------------------------------------|----------------------------------------------------------------------------------|

| OKAY         | Access completed normally                  |                                                                                  |

| ERROR        | Slave aborts access,<br>(2 cycle response) | Master has option of continuing or<br>terminating a burst containing an<br>ERROR |

It is permissible to continuously drive HRESP Low in a system which does not wish to generate any errors.

### **ERROR** Response

If HRESP = ERROR, CM0-DS takes an exception and you should implement appropriate exception handler to catch the error

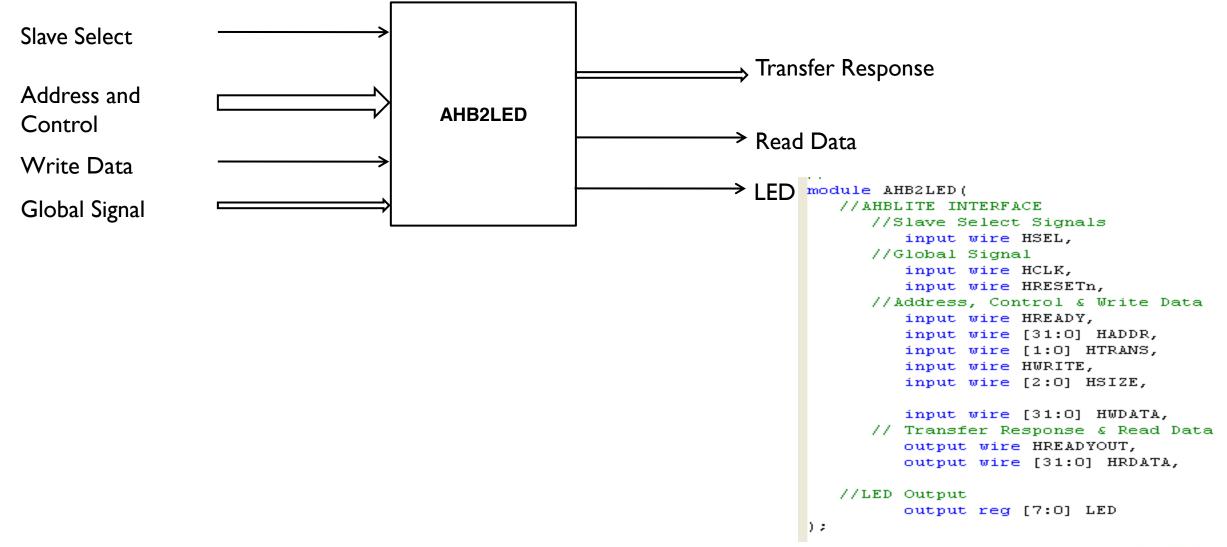

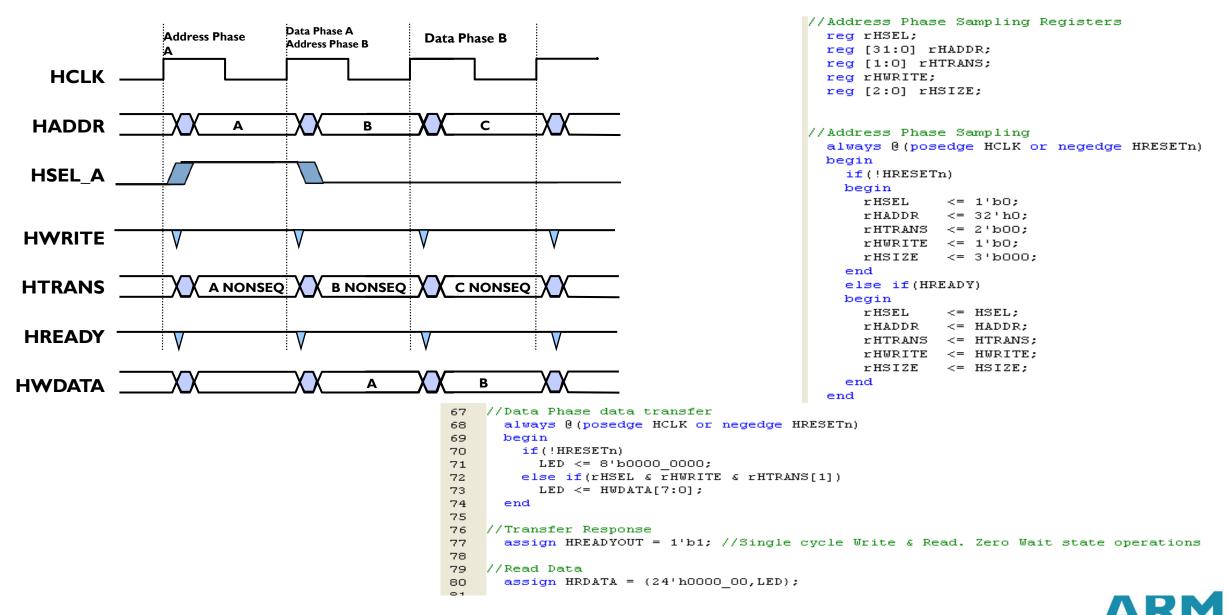

# A simple AHB-Lite Slave

AHB2LED.v

## AHB2LED TOP LEVEL

## Sampling Address & Control

end

# Sampling Address & Control

### Lab

- Analyse the AHB2LED.v file provided

- In the next lab, we will look into system integration, simulation and implementation of a complete AHB-Lite System using Cortex M0 Design Start core