Task:

# Design and Implement a Novel 16-bit Microprocessor in $0.35\mu m$ CMOS (C035U)

- Complete IC Design Flow

- Complex System

- Importance of Systematic Approach

- Modular Design & Test

- Manage Complexity through Hierarchy

- Team Exercise

## Milestones

| 1. | Research  | Document |

|----|-----------|----------|

| ㅗ• | ICOCAICIL |          |

WED week 4 (19<sup>th</sup> February 2014)

• Report on Preliminary Research

2. Initial Design

WED week 5 (26<sup>th</sup> Feb 2014)

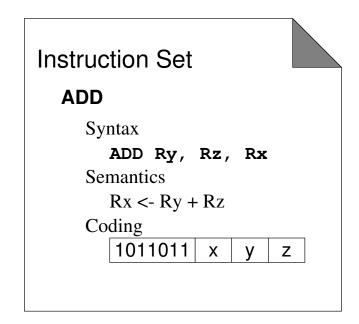

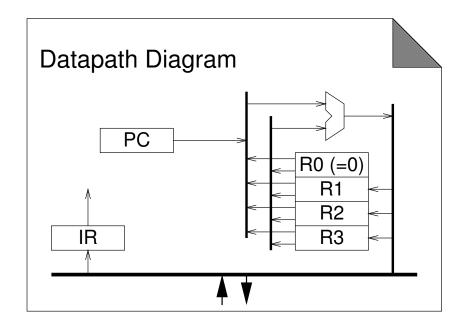

• Instruction Set, Datapath Diagram

3. Behavioural Model

WED week 6 (5<sup>th</sup> March 2014)

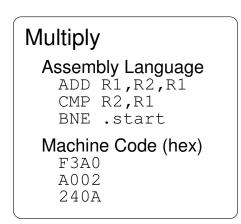

• SystemVerilog

4. Cross Simulation

WED week 7 (12<sup>th</sup> March 2014)

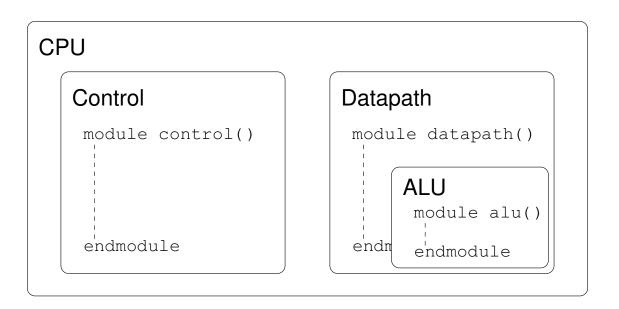

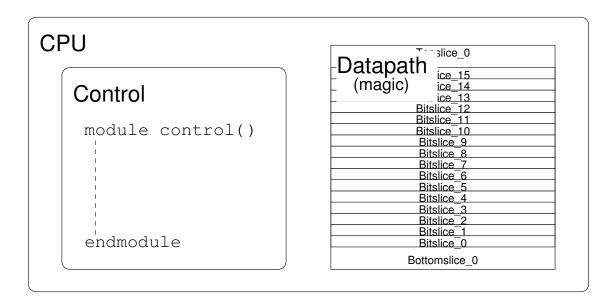

• SystemVerilog Control Unit, Magic Datapath

5. Final Design

FRI week 10 (2<sup>nd</sup> May 2014)

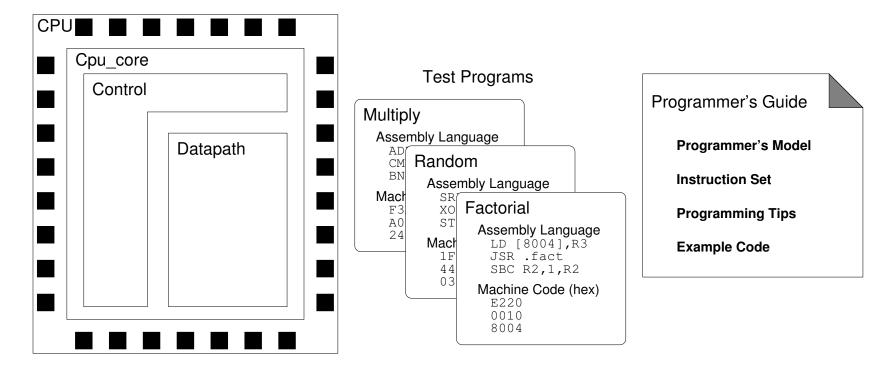

• Full Magic Design, Programmer's Guide

6. Project Report

Tue week 12 (13<sup>th</sup> May 2014)

• Report on Design and Implementation

## Initial Design

#### Behavioural Model

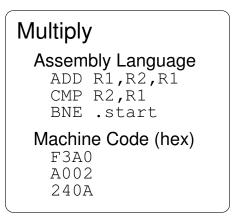

#### Test Program

#### **Cross Simulation**

#### Test Program

The submitted SystemVerilog control module may well be a newer version than that submitted with the behavioural model, in which case a newer SystemVerilog datapath module must also be submitted.

### Final Design

An updated SystemVerilog behavioural model of the processor must be submitted with the final design.

| week | MON | TUE     | WED         | THU | mini milestones          | FRI          |

|------|-----|---------|-------------|-----|--------------------------|--------------|

| 1    |     |         |             | LAB | Confirm Teams            |              |

| 2    |     |         |             | LAB | Declaration of           |              |

|      |     |         |             |     | Specialisms              |              |

| 3    |     |         |             | LAB | t.b.a.                   |              |

| 4    |     |         | Research    | LAB | Draft Design             |              |

|      |     |         | Report      |     |                          |              |

| 5    |     |         | Initial     | LAB | Initial Behavioural      |              |

|      |     |         | Design      |     | Model (executes at least |              |

|      |     |         |             |     | 4 instructions)          |              |

| 6    |     |         | Behavioural | LAB | Simulation of Basic      | Behavioural  |

|      |     |         | Model       |     | Datapath (including      | Model with   |

|      |     |         |             |     | ALU and Data Registers)  | Interrupts   |

| 7    |     |         | Cross       | LAB | Simulation of Placed     |              |

|      |     |         | Simulation  |     | and Routed Control Unit  |              |

| 8    |     |         |             | LAB | t.b.a.                   |              |

| 9    |     |         |             | LAB | Simulation of First Cut  |              |

|      |     |         |             |     | Chip in Pad Ring         |              |

| 10   |     |         |             | LAB | t.b.a.                   | Final Design |

| 11   |     |         |             |     |                          |              |

| 12   |     | Project |             |     |                          |              |

|      |     | Report  |             |     |                          |              |

# ELEC6027 VLSI Design Project Thursday Lectures

| Week | Time  | Topic                                                       |

|------|-------|-------------------------------------------------------------|

| 1    | 10:00 | Introduction                                                |

|      |       | This lecture                                                |

| 2    | 10.00 | Pasia Dragoson Dosion                                       |

|      | 10:00 | Basic Processor Design                                      |

|      |       | Including RISCish and CISCish examples                      |

| 3    | 10:00 | Processor Datapath Design                                   |

|      |       | Including RISCish and CISCish example                       |

| 4    | 10:00 | Behavioural Modelling                                       |

|      |       | This seminar is intended for SystemVerilog specialists only |

| 5    | 10:00 | Advanced Bitslice Design                                    |

|      |       | This seminar is intended for Datapath specialists only      |