# Components for Logic

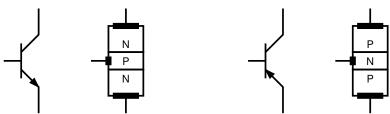

#### **MOS Transistors**

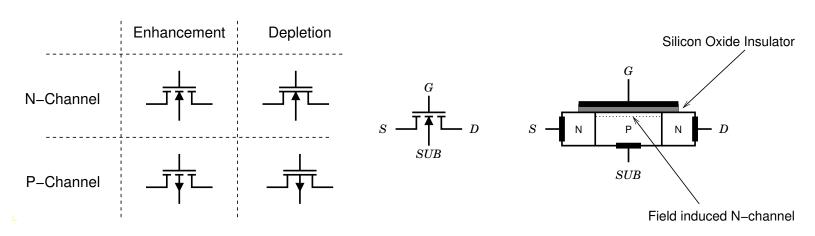

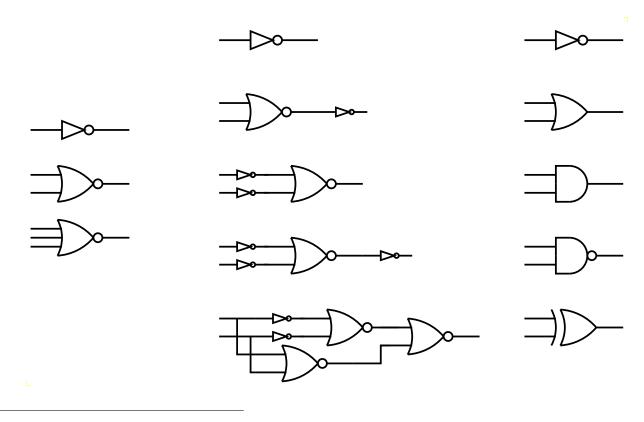

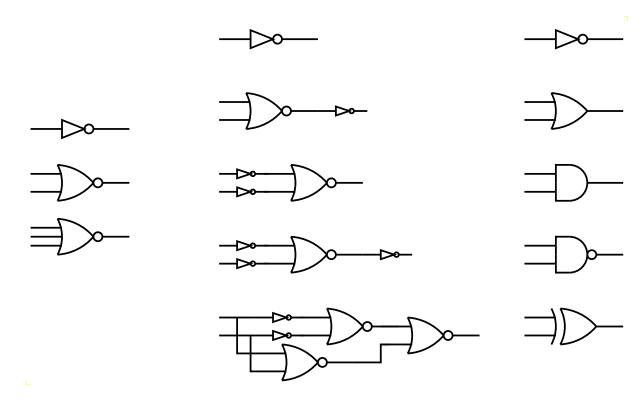

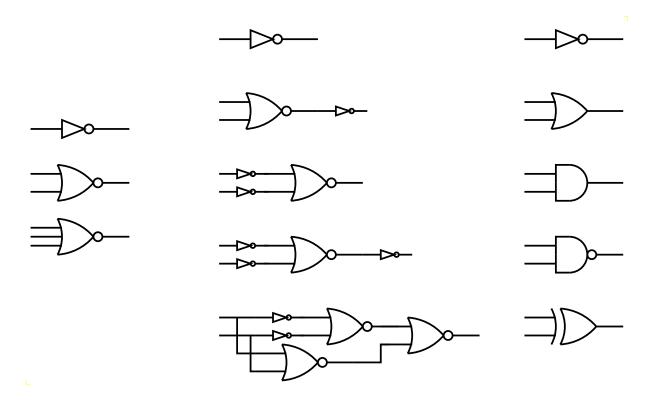

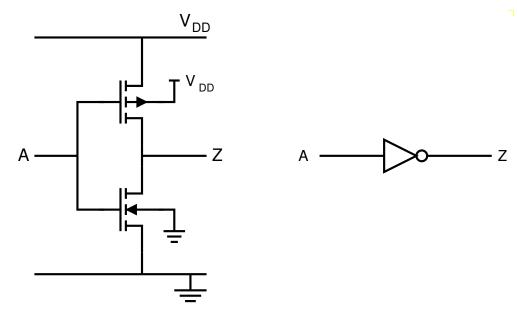

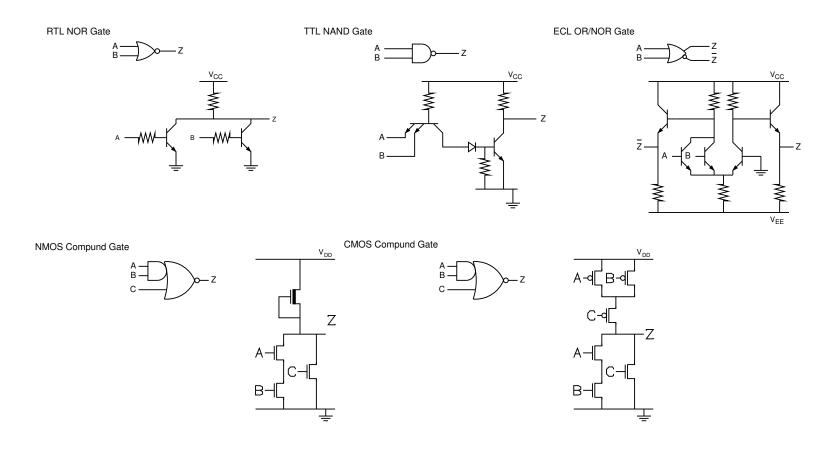

RTL Inverter and NOR gate

All functions can be realized using only the NOR gates<sup>1</sup> available in the RTL logic family.<sup>2</sup>

2

<sup>&</sup>lt;sup>1</sup>Note that an inverter is a special case of a NOR gate with only one input.

<sup>&</sup>lt;sup>1</sup>Note that an inverter is a special case of a NOR gate with only one input.

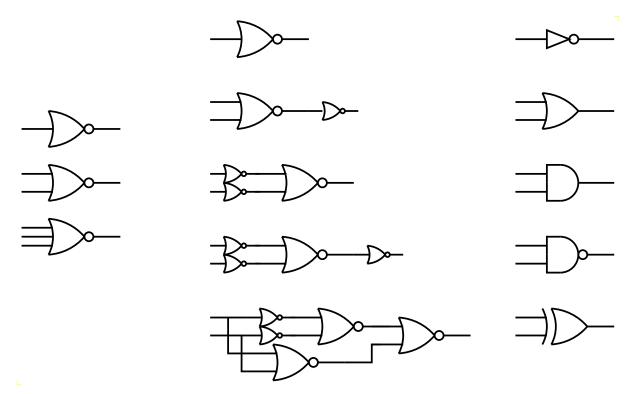

<sup>&</sup>lt;sup>1</sup>Note that an inverter is a special case of a NAND gate with only one input.

<sup>&</sup>lt;sup>2</sup>NAND gates could be used instead for logic families which support only NAND gates.

<sup>&</sup>lt;sup>1</sup>Note that an inverter is a special case of a NOR gate with only one input.

<sup>&</sup>lt;sup>2</sup>NAND gates could be used instead for logic families which support only NAND gates.

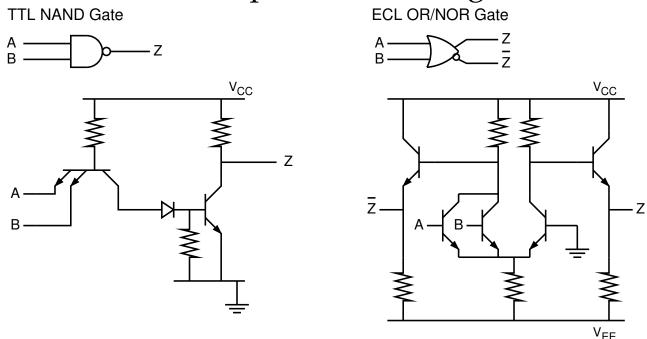

## Other Bipolar Technologies

- TTL gives faster switching than RTL at the expense of greater complexity<sup>3</sup>. The characteristic multi-emitter transistor reduces the overall component count.

- ECL is a very high speed, high power, non-saturating technology.

<sup>&</sup>lt;sup>3</sup>Most TTL families are more complex than the basic version shown here

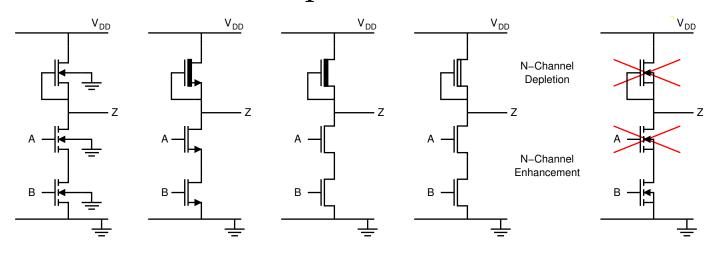

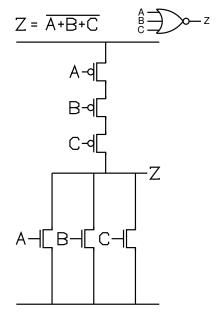

NMOS - a VLSI technology.

- Circuit function determined by series/parallel combination of devices.

- Depletion transistor acts as non-linear load resistor.

Resistance increases as the enhancement device turns on, thus reducing power consumption.

- The low output voltage is determined by the size ratio of the devices.

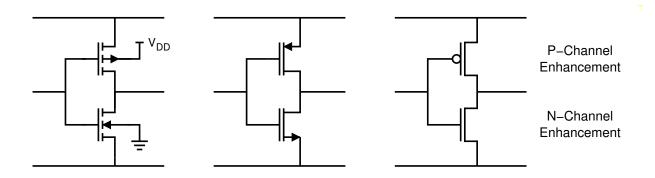

#### Alternative transistors representations for NMOS circuits

Various shorthands are used for simplifying NMOS circuit diagrams.

- Substrate connections need not be drawn since all must connect to Gnd.

- Since source and drain are indistinguishable in the layout, there is no need to show the source on the circuit diagram.

Note that schematic tools not designed for IC design will usually include inappropriate 3-terminal symbols.

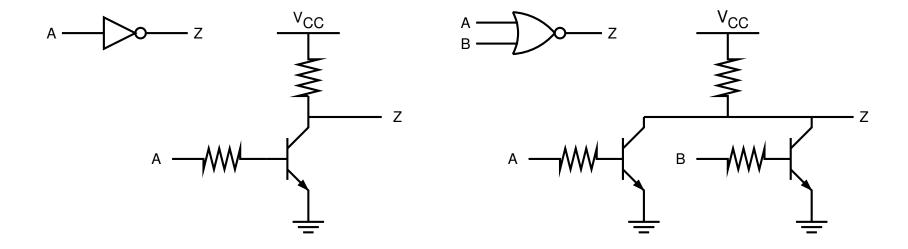

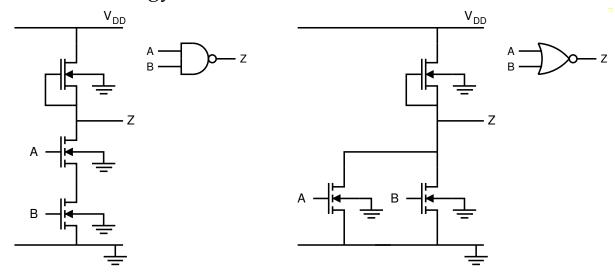

# CMOS logic

CMOS - state of the art VLSI.

- An active PMOS device complements the NMOS device giving:

- rail to rail output swing.

- negligible static power consumption.

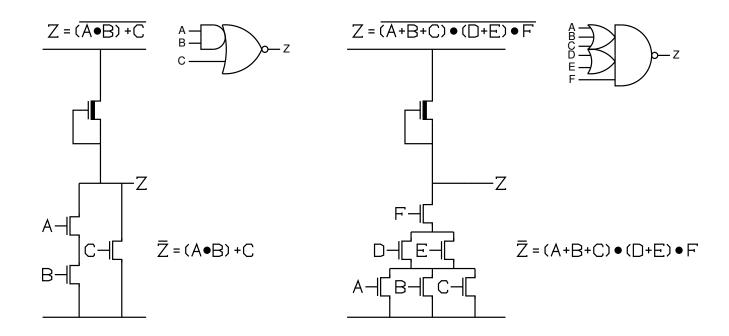

#### Alternative transistor representations for CMOS circuits

Digital CMOS circuits<sup>4</sup> tend to use simplified symbols like their NMOS counterparts.

- In general substrate connections are not drawn where they connect to Vdd (PMOS) and Gnd (NMOS).

- All CMOS devices are enhancement mode.

- Transistors act as simple digitally controlled switches.

<sup>&</sup>lt;sup>4</sup>in analog CMOS circuits we may have wells not connected to Vdd/GND

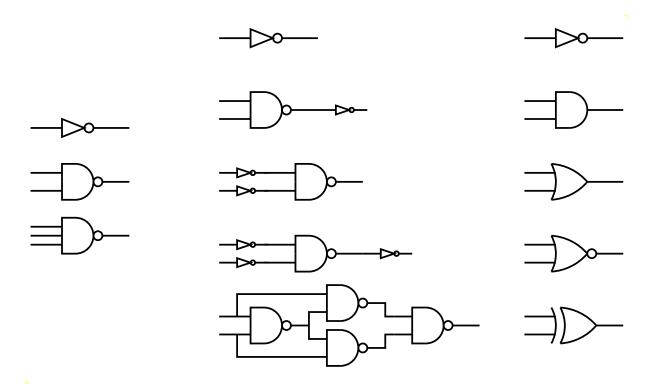

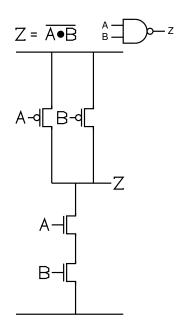

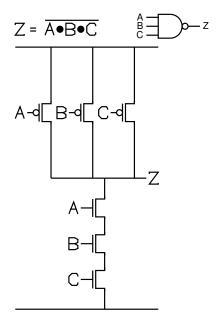

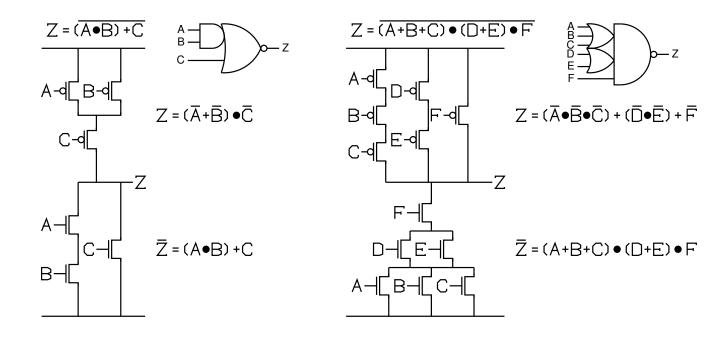

#### Static CMOS complementary gates

• For any set of inputs there will exist either a path to Vdd or a path to Gnd.

# **Compound Gates**

- All compound gates are inverting.

- Realisable functions are arbitrary AND/OR expressions with inverted output.

# Compound Gates

- All compound gates are inverting.

- Realisable functions are arbitrary AND/OR expressions with inverted output.

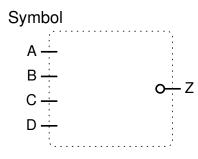

# Compound Gate Example

$$Z = (\overline{A \bullet B}) + (C \bullet D)$$

Pull Up Network

$$Z = \int (\overline{A}, \overline{B}, \overline{C}, \overline{D})$$

$$Z =$$

\_\_\_\_\_ Z

$V_{DD}$

Pull Down Network

$$\overline{Z} = \int (A,B,C,D)$$

$\overline{Z} = (A \bullet B) + (C \bullet D)$

GND

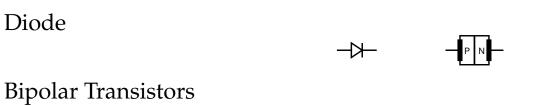

• Bipolar Transitors with Resistors - MSI/LSI

RTL - NOR

TTL - NAND

ECL - OR/NOR

• MOS Transistors (no resistors) - VLSI

**NMOS**

CMOS - No static power!

Both allow construction of NOR, NAND & Compound gate (always inverting)