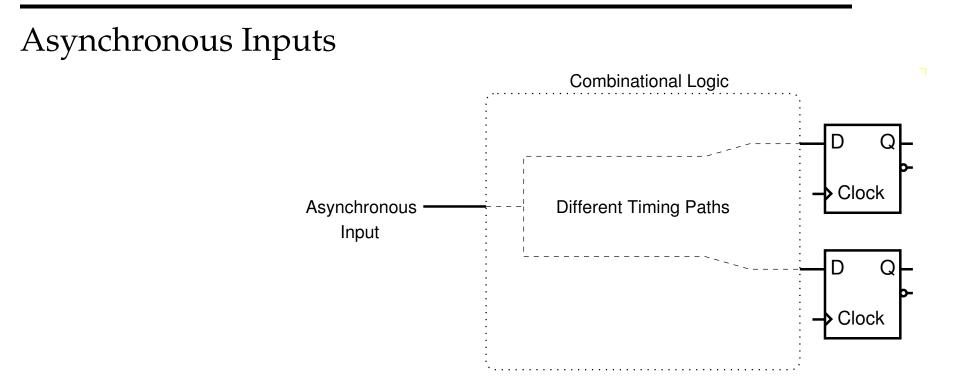

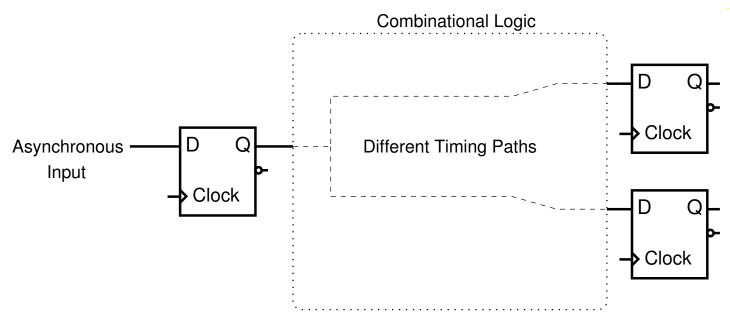

With different timing paths through combinational logic, we can get unexpected results.

Asynchronous Inputs

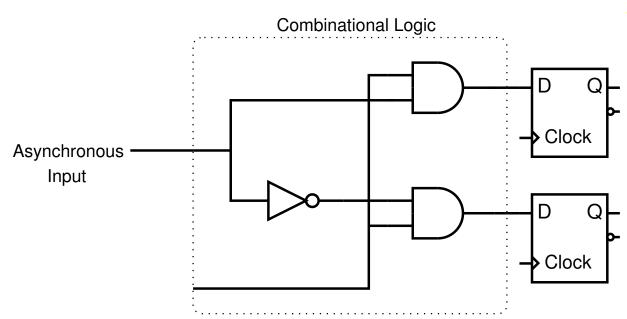

With different timing paths through combinational logic, we can get unexpected results.

In this example, a falling input we may be registered as neither high nor low.

21002

Asynchronous Inputs Combinational Logic Asynchronous — D Q Different Timing Paths Input

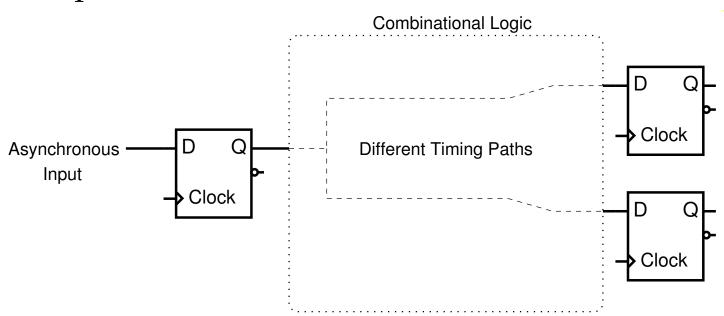

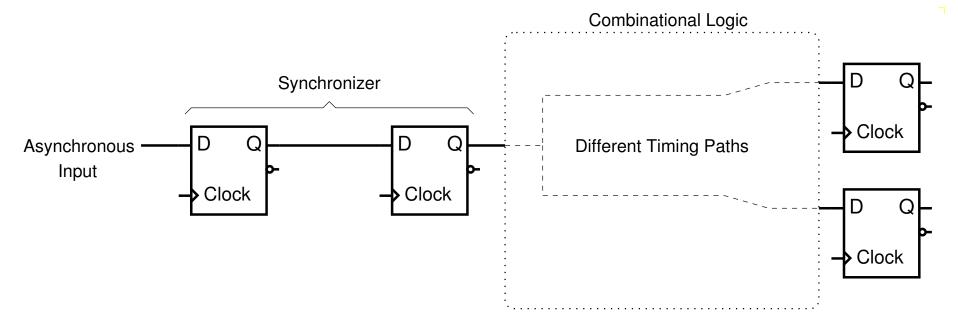

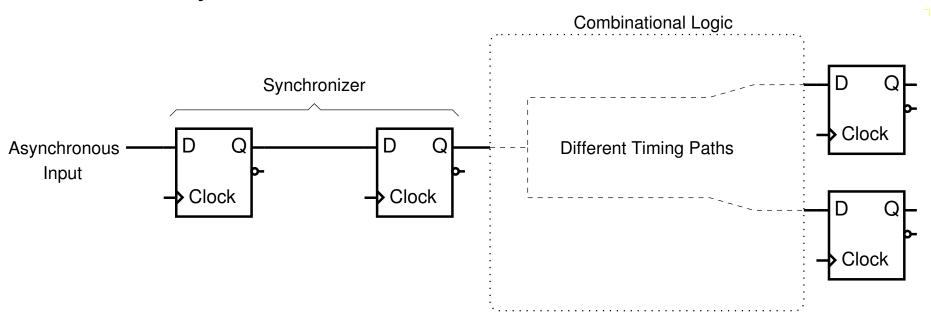

Retiming the asynchronous input before the combinational logic block should give more predictable results.

Asynchronous Inputs

Retiming the asynchronous input before the combinational logic block should give more predictable results.

21004

Asynchronous Inputs

To avoid a setup violation<sup>1</sup>:

$ClockPeriod > t_{pQ} + t_{critical\_path} + t_{setup}$

<sup>1</sup>assuming ideal clock

Asynchronous Inputs

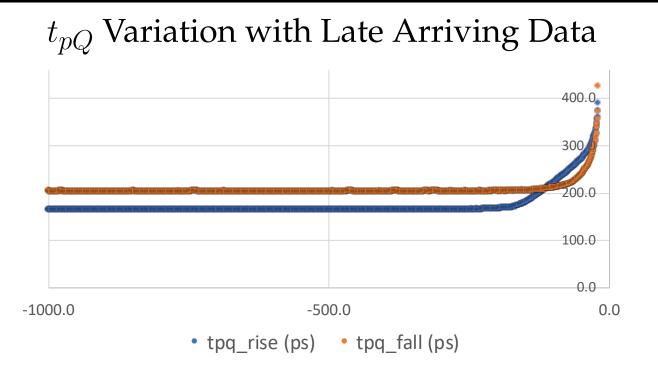

To avoid a setup violation<sup>1</sup>:

$ClockPeriod > t_{pQ} + t_{critical\_path} + t_{setup}$

but  $t_{pQ}$  may now be unpredictable

<sup>1</sup>assuming ideal clock

- As the setup time (*t<sub>setup</sub>*) is reduced (close to it's absolute minimum value), the clock-to-Q delay (*t<sub>pQ</sub>*) increases sharply.

- A flip-flop dasheet will quote a  $t_{pQ}$  value for a minimum  $t_{setup}$  value. When we violate the minimum specified  $t_{setup}$  value, the quoted  $t_{pQ}$  value is no longer valid.

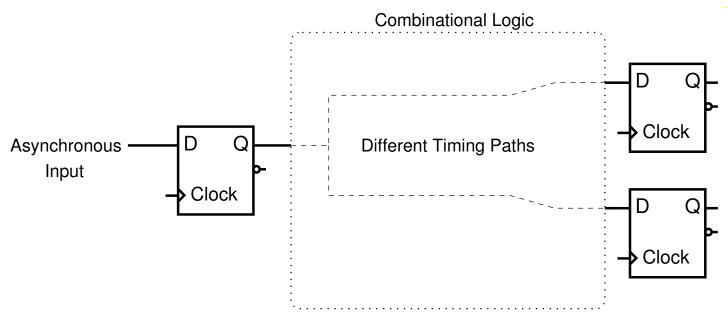

## Asynchronous Inputs

A second flip-flop in the synchronizer gives a predictable  $t_{pQ}$  for our equation:

$$ClockPeriod > t_{pQ} + t_{critical\_path} + t_{setup}$$

21008

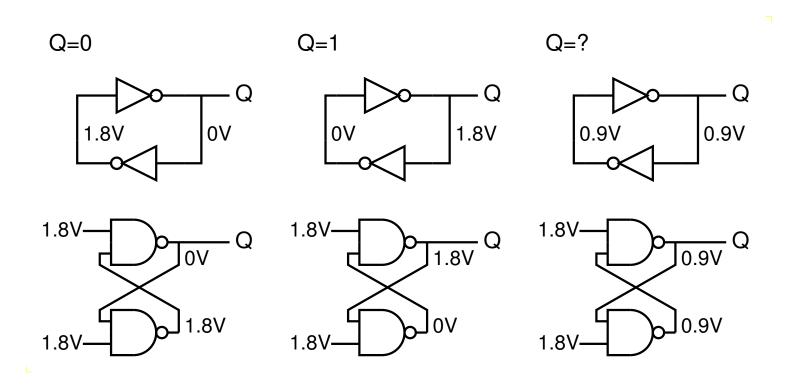

Flip-Flop Stable States

The third state is described as *metastable* since a slight perturbation in one of the 50%-of- $V_{DD}$  voltages will result in a move to one of the other states.

Metastability

- The first flip-flop in our synchronizer may go metastable in the extreme case where the set-up time for D is reduced and *t*<sub>pQ</sub> increases.

- The two flip-flop synchronizer gives a full clock cycle for the metastable state to resolve itself into one or other normal state.

## Summary