# Complex Instruction Set Computers

### CISC

Successors to the 6809 have continued to follow CISC philosophy.

- More registers

- More instructions

- More powerful instructions

- More addressing modes

Each improvement reduces the number of slow memory accesses made by the processor.

# Reduced Instruction Set Computers

#### **RISC**

#### New Philosophy

- Invest effort and chip area in accelerating commonly used instructions.

- We can build a chip with slimmed down instruction set which clocks faster.

- Common instructions execute faster.

- Efficient compilers should be easier to write for a simpler instruction set.

Most implementations aim for 1 cycle per instruction although now we see machines with multiple execution units aiming for even greater throughput.

# Reduced Instruction Set Computers

## **SPARC**

- Scalable Processor ARChitecture

- Developed by Sun Microsystems

- Open architecture

- Owned by SPARC international

- Used in

- Sun SPARCstations

- other computers including CM-5

- embedded microcontroller systems

- ECS microprocessor lab

• Register / Register architecture

• Most instructions will either reference three registers or two registers and one immediate.

- ADD

$$\$20,\$17,\$5$$

reg5  $\leftarrow$  reg20 + reg17

- LD  $[\$11+\$12],\$5$  reg5  $\leftarrow$  [reg11 + reg12]

- SLL  $\$2,13,\$5$  reg5  $\leftarrow$  reg2 >> 13

• All instructions are 32 bits wide.

| out    | r15 | (07) | temp                 |

|--------|-----|------|----------------------|

|        | r14 | (SP) | stack pointer        |

|        | r13 | (05) | outgoing param reg 5 |

|        | r12 | (04) | outgoing param reg 4 |

|        | r11 | (03) | outgoing param reg 3 |

|        | r10 | (o2) | outgoing param reg 2 |

|        | r9  | (o1) | outgoing param reg 1 |

|        | r8  | (00) | outgoing param reg 0 |

| global | r7  | (g7) | global 7             |

|        | r6  | (g6) | global 6             |

|        | r5  | (g5) | global 5             |

|        | r4  | (g4) | global 4             |

|        | r3  | (g3) | global 3             |

|        | r2  | (g2) | global 2             |

|        | r1  | (g1) | global 1             |

|        | r0  | (g0) | 0                    |

| in    | r31 | (i7) | return address       |

|-------|-----|------|----------------------|

|       | r30 | (FP) | frame pointer        |

|       | r29 | (i0) | incoming param reg 5 |

|       | r28 | (i0) | incoming param reg 4 |

|       | r27 | (i0) | incoming param reg 3 |

|       | r26 | (i0) | incoming param reg 2 |

|       | r25 | (i0) | incoming param reg 1 |

|       | r24 | (i0) | incoming param reg 0 |

| local | r23 | (17) | local 7              |

|       | r22 | (16) | local 6              |

|       | r21 | (15) | local 5              |

|       | r20 | (14) | local 4              |

|       | r19 | (13) | local 3              |

|       | r18 | (12) | local 2              |

|       | r17 | (11) | local 1              |

|       | r16 | (10) | local 0              |

note that g0 is a dummy register; it is always zero.

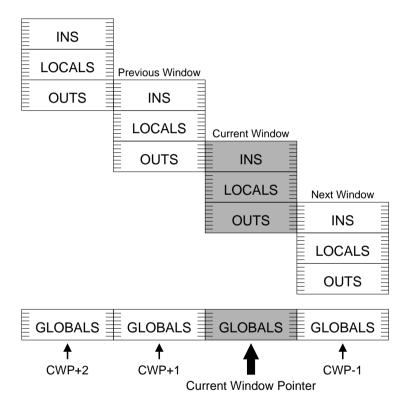

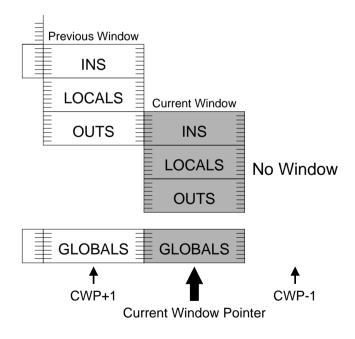

• The 32 registers visible to the program are merely a window on those available.

• The current window pointer determines which register sets appear in this window.

• A subroutine call is normally combined with a context change, giving access to a new window.<sup>1</sup>

• Parameters to be passed to a subroutine are set up using the **OUT** registers which become the **IN** registers of the subroutine.

<sup>&</sup>lt;sup>1</sup>Due to the wonders of pipelining the SAVE is placed after the CALL and is executed anyway

• A return from subroutine uses JMPL to indirect via the stored return address and RESTORE to recover the old register window.

JMPL %i7 + 8, %0

$$\$0 \leftarrow PC$$

$$PC \leftarrow nPC$$

$$nPC \leftarrow \$i7 + 8$$

$$RESTORE$$

$$CWP \leftarrow CWP + 1$$

$$PC \leftarrow nPC$$

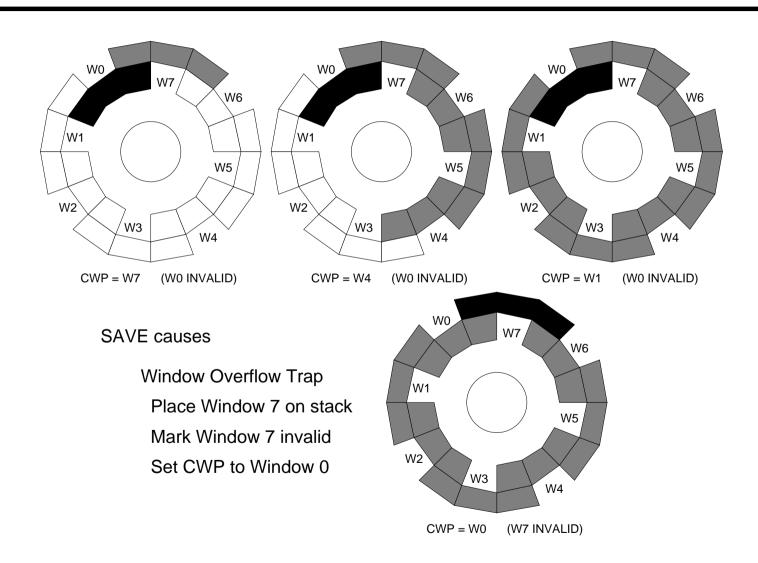

### Window Overflow

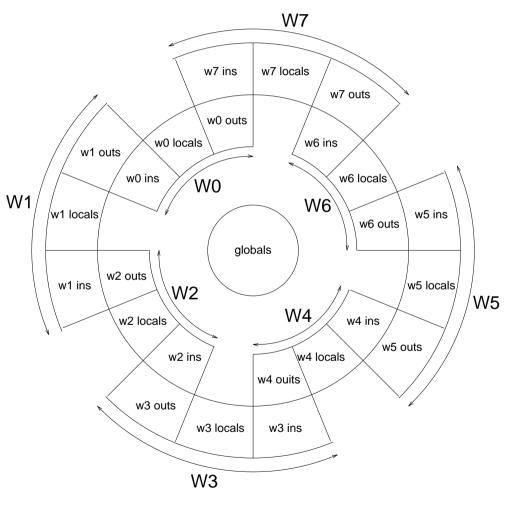

The Scalable architecture of the SPARC allows the manufacturer to choose how many windows exist on the chip. Since this number is going to be finite, we must allow for the possibility of window overflow.

• Windows are arranged in a circle.

Up to seven full windows (including ins and outs) are supported by the eight window circular stack. Initially the Current Window Pointer may be set to W7 and the W0 window marked as invalid. The program may use all windows W7-W1 without any problems.

- A SAVE instruction which attempts to allocate the invalid window results in a *window\_overflow* trap.

- The trap routine is responsible for saving the contents of the oldest window to an *old window stack* in memory.

- The trap routine will also change the Window Invalid Mask to indicate a new invalid window.

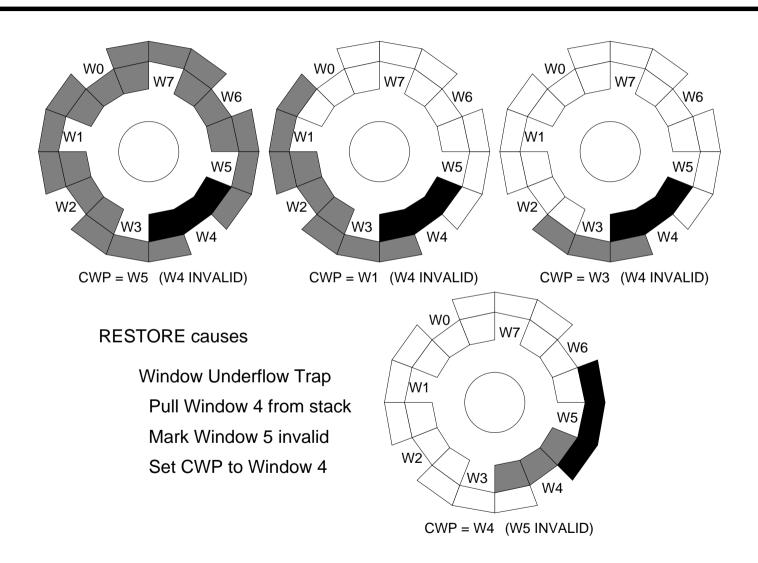

- A RESTORE instruction which attempts to allocate the invalid window results in a *window\_underflow* trap.

- The trap routine will pull a window from the *old window stack* into the correct register positions.